7368868E STMicroelectronics Confidential 31/709

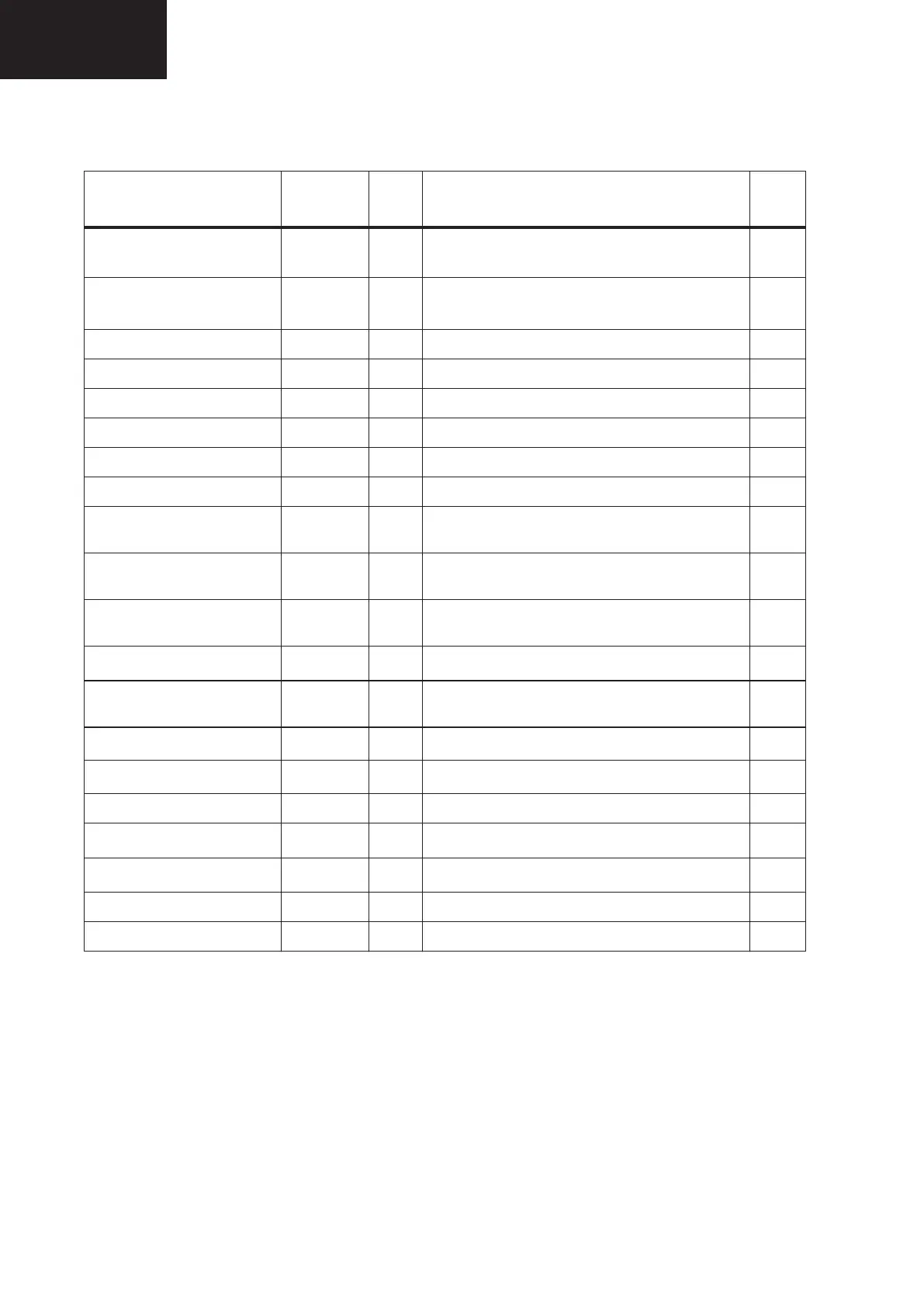

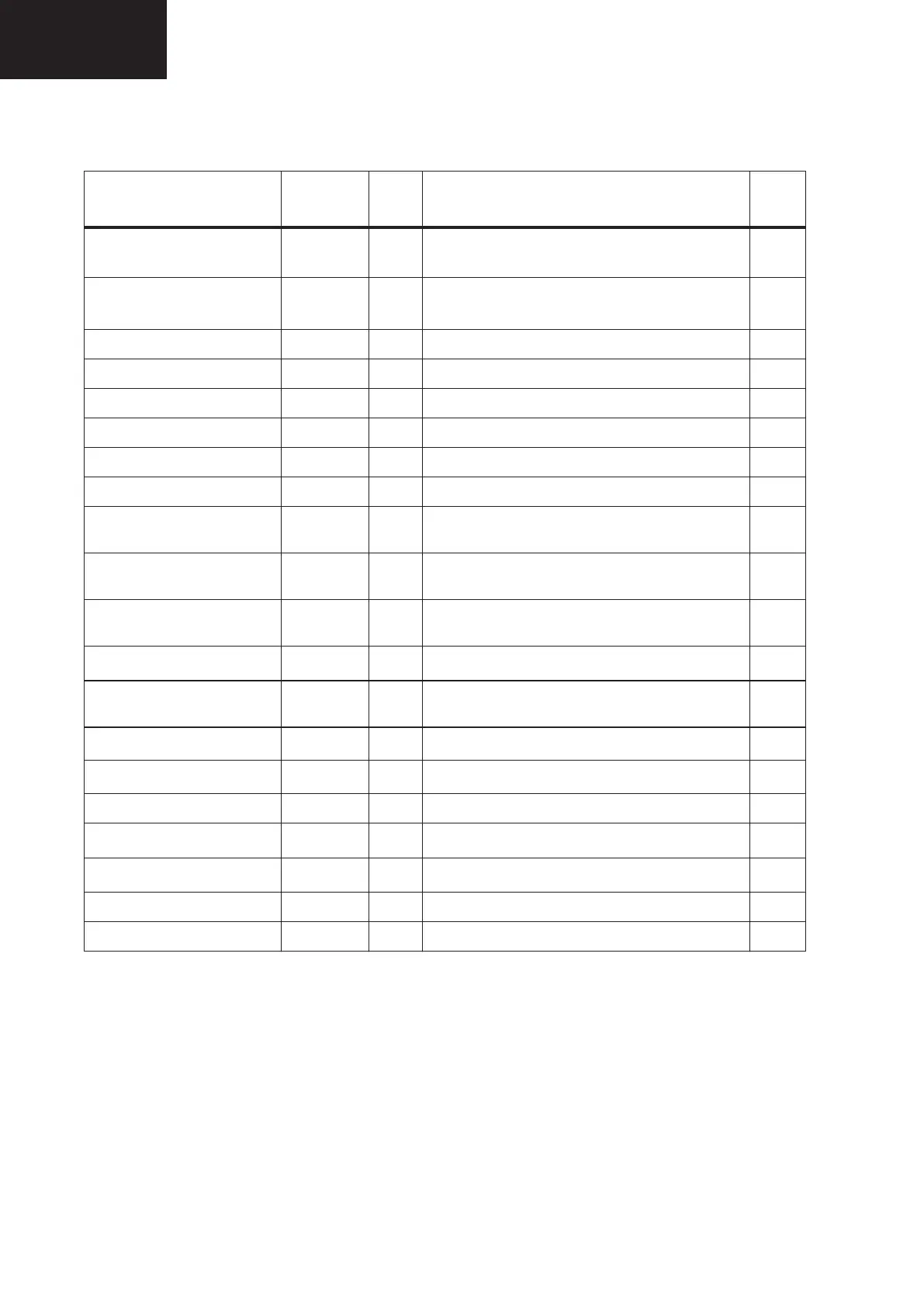

STi5516 Pin list

Confidential

Table 9: EMI pins

Pin Location I/O Function

Pad

type

NOT_EMIRAS or

NOT_CI_IORD

a

J2 O Row address strobe for SDRAM C4

NOT_EMICAS or

NOT_CI_IOW

a

J1 O Column address strobe for SDRAM E8

NOT_EMICSA K4 O Peripheral chip select A E8

NOT_EMICSB K3 O Peripheral chip select B E8

NOT_EMICSC K2 O Peripheral chip select C E8

NOT_EMICSD K1 O Peripheral chip select D E8

NOT_EMICSE L4 O Peripheral chip select E E8

NOT_EMICSF L3 O Peripheral chip select F E8

NOT_EMIBE[1:0] L1, L2 O External device data bus byte enable. 1 bit per

byte of the data bus.

E8

NOT_EMIOE or

NOT_CI_OE

M1 O External device output enable. E8

NOT_EMILBA or

NOT_CI_WEA

N3 O Flash device load burst address. E8

EMIWAITNOTTREADY

b

N4 I External memory device target ready indicator C4

EMIRDNOTWR N2 O External read/write access indicator. Common to

all devices.

E8

EMIDATA[15:0]

c

I/O External common data bus. E8

EMIADDR[25:2]

d e

O External common address bus E8

NOT_EMIREQGNT J3 O Bus request/grant indicator E8

NOT_EMIACKREQ

b

H1 I Bus grant/request indicator C4

EMIBOOTMODE0

b

H3 I External power-up port size indicator C4

EMISDRAMCLK A1 O SDRAM clock E8

EMIFLASHCLK A2 O Peripheral clock E8

a. Or equivalent ATA HDD interface signal.

b. 5 V tolerant

c. B3, A3, A4, B4, C4, A5, B5, C5, A6, B6, C6, D6, A7, B7, C7 and A8.

d. EMIADDR[19:20] are used as ATA HDD interface function: ATA CS0 and CS1. There is no

interconnect configuration control register bit to select this function. The addresses are just

reused as chip selects.

e. B8, C8, A9, B9, C9, D9, A10, B10, C10, A11, B11, C11, A12, B12, C12, D12, A13, B13, C13,

D13, A14, B14, C14 and D14.

Loading...

Loading...