SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 103 Version 1.5

The I2C slave address.

ADD[9:0] is valid when ADD_MODE = 1.

ADD[7:1] is valid when ADD_MODE = 0.

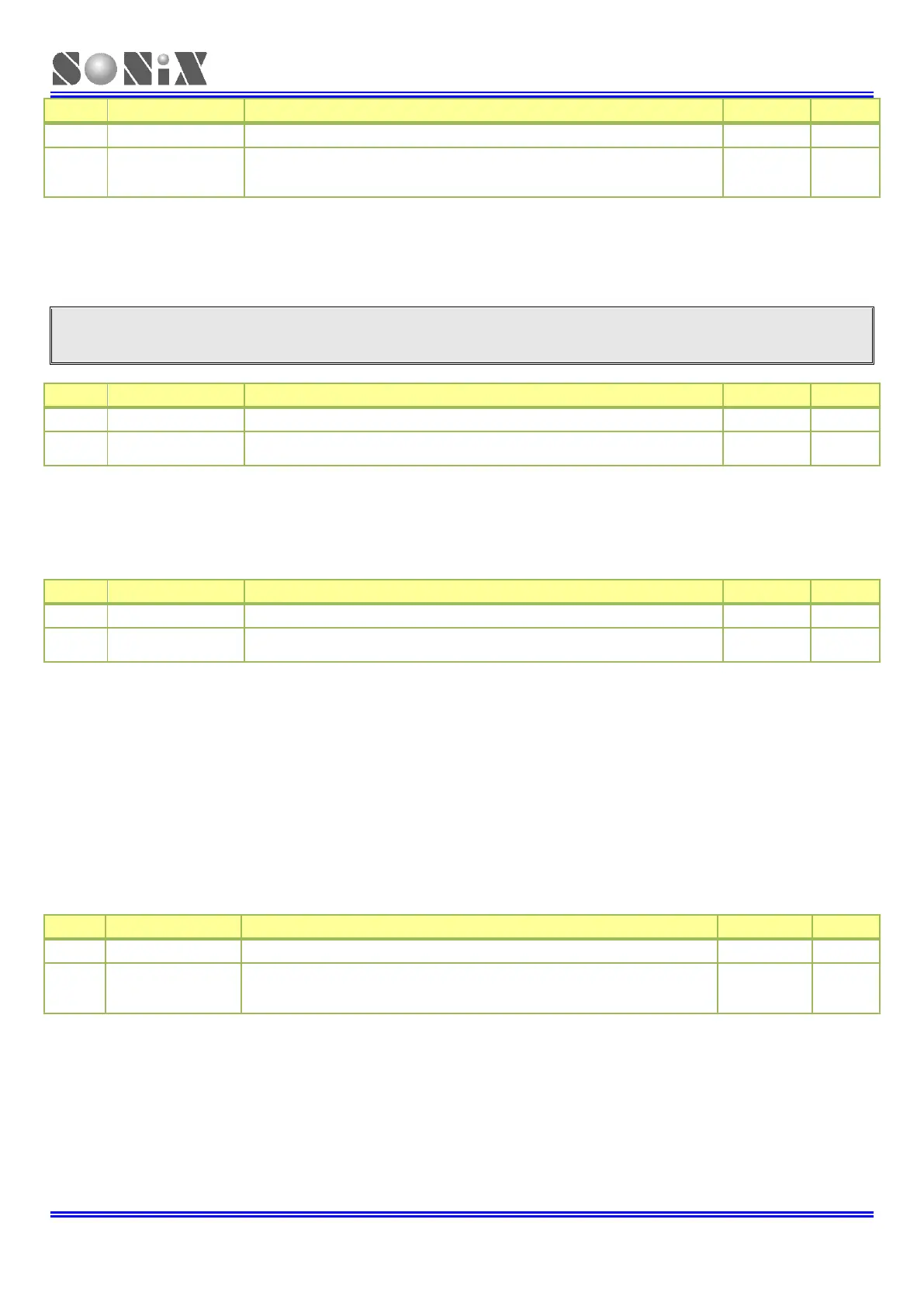

9.7.7 I2C n SCL High Time register (I2Cn_SCLHT) (n=0)

Address Offset: 0x20

Note: I2C Bit Frequency = I2Cn_PCLK / (I2Cn_SCLHT+I2Cn_SCLLT)

Count for SCL High Period time.

SCL High Period Time = (SCLH+1) * I2C0_PCLK cycle

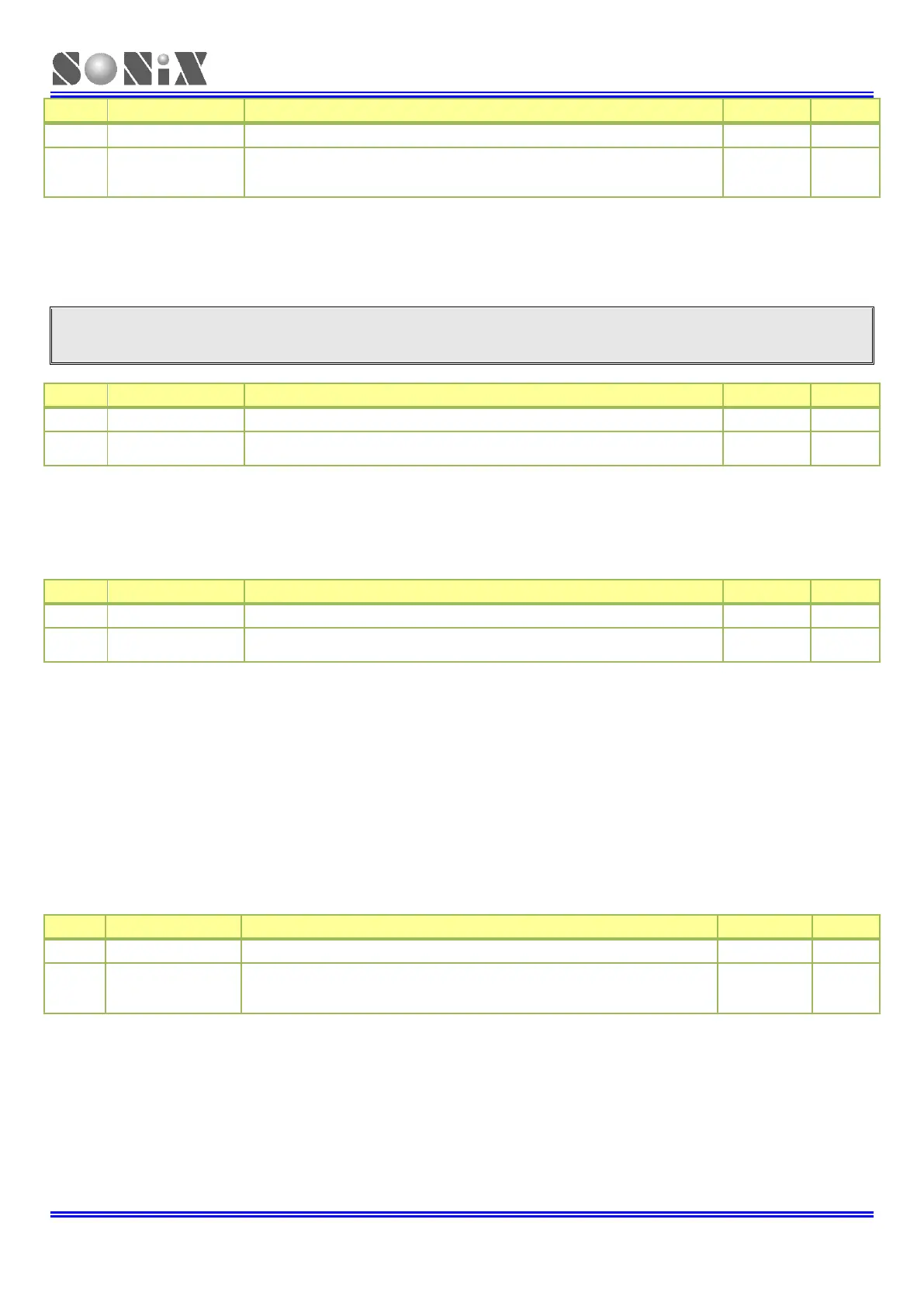

9.7.8 I2C n SCL Low Time register (I2Cn_SCLLT) (n=0)

Address Offset: 0x24

Count for SCL Low Period time.

SCL Low Period Time = (SCLL+1) * I2C0_PCLK cycle.

9.7.9 I2C n Timeout Control register (I2Cn_TOCTRL) (n=0)

Address Offset: 0x2C

Timeout happens when Master/Slave SCL remained LOW for:

TO * 32 * I2C0_PCLK cycle.

When I2C timeout occurs, the I2C transfer will return to “IDLE” state and issue a TO interrupt to inform user. That

means SCL/SDA will be released by HW after timeout. User can issue a STOP after timeout interrupt occurred in

Master mode.

Time-out status will be cleared automatically by writing I2Cn_CTRL or I2Cn_TXDATA register.

Count for checking Timeout.

0: Disable Timeout checking.

N: Timeout period time = N*32*I2Cn_PCLK cycle.

Loading...

Loading...