SN32F260 Series

32-Bit Cortex-M0 Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 76 Version 1.5

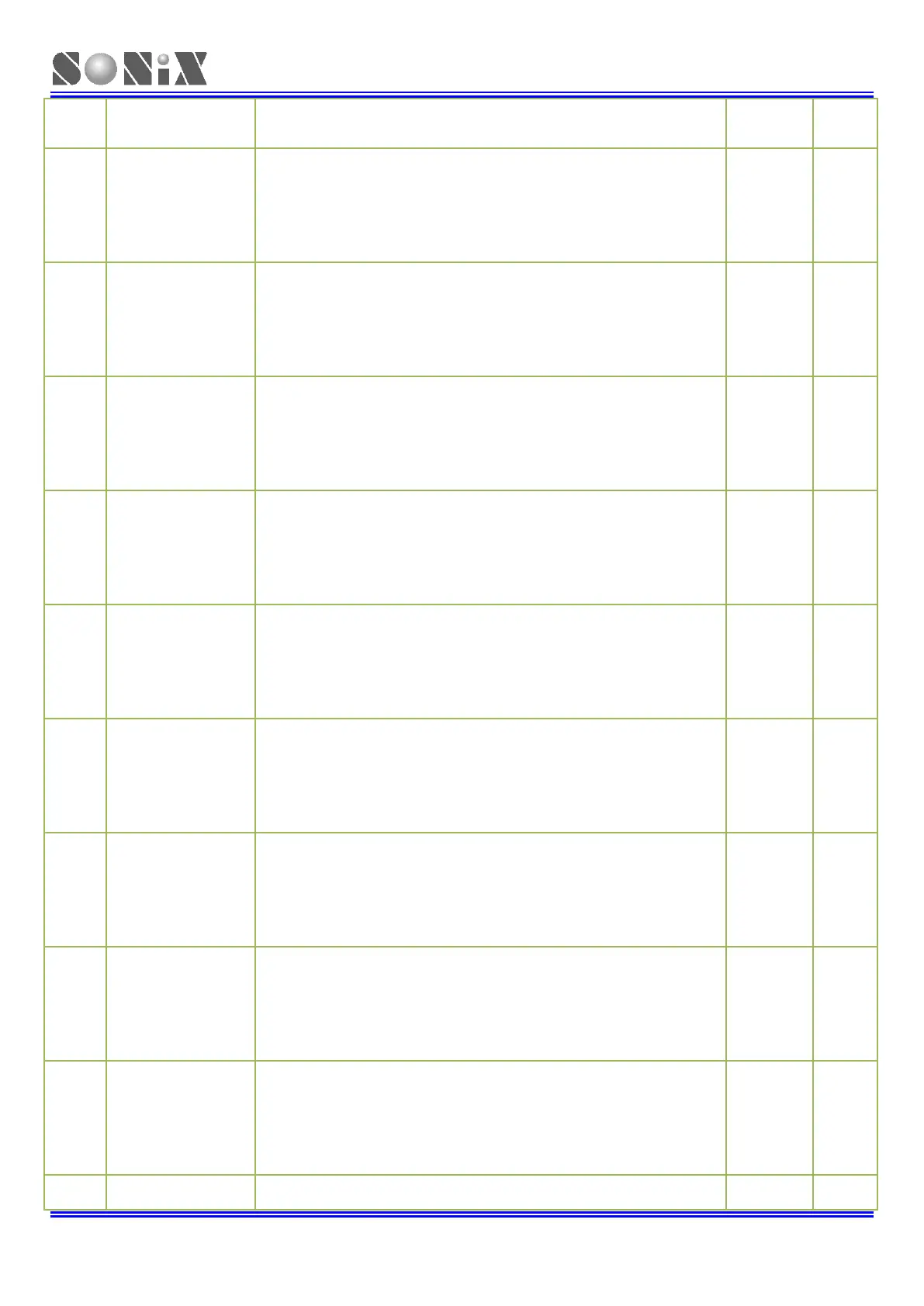

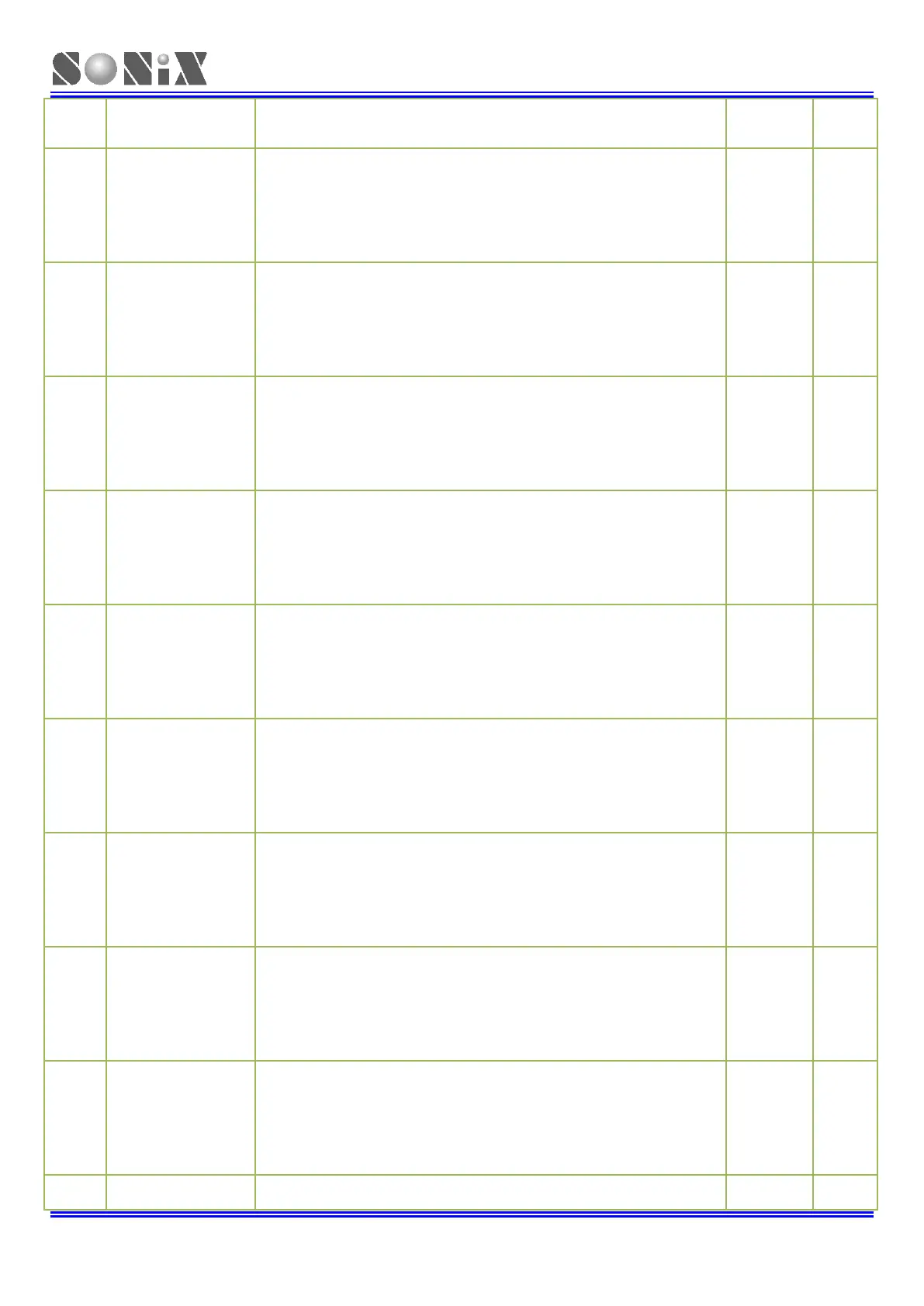

PWM11 is 1 when TC<MR11 during Up-counting period.

10: PWM11 is forced to 0.

11: PWM11 is forced to 1.

PWM10 output.

00: PWM mode 1.

PWM10 is 0 when TC<MR10 during Up-counting period.

01: PWM mode 2.

PWM10 is 1 when TC<MR10 during Up-counting period.

10: PWM10 is forced to 0.

11: PWM10 is forced to 1.

PWM9 output.

00: PWM mode 1.

PWM9 is 0 when TC<MR9 during Up-counting period.

01: PWM mode 2.

PWM9 is 1 when TC<MR9 during Up-counting period.

10: PWM9 is forced to 0.

11: PWM9 is forced to 1.

PWM8 output.

00: PWM mode 1.

PWM8 is 0 when TC<MR8 during Up-counting period.

01: PWM mode 2.

PWM8 is 1 when TC<MR8 during Up-counting period.

10: PWM8 is forced to 0.

11: PWM8 is forced to 1.

PWM7 output.

00: PWM mode 1.

PWM7 is 0 when TC<MR7 during Up-counting period.

01: PWM mode 2.

PWM7 is 1 when TC<MR7 during Up-counting period.

10: PWM7 is forced to 0.

11: PWM7 is forced to 1.

PWM6 output.

00: PWM mode 1.

PWM6 is 0 when TC<MR6 during Up-counting period.

01: PWM mode 2.

PWM6 is 1 when TC<MR6 during Up-counting period.

10: PWM6 is forced to 0.

11: PWM6 is forced to 1.

PWM5 output.

00: PWM mode 1.

PWM5 is 0 when TC<MR5 during Up-counting period.

01: PWM mode 2.

PWM5 is 1 when TC<MR5 during Up-counting period.

10: PWM5 is forced to 0.

11: PWM5 is forced to 1.

PWM4output.

00: PWM mode 1.

PWM4 is 0 when TC<MR4 during Up-counting period.

01: PWM mode 2.

PWM4 is 1 when TC<MR4 during Up-counting period.

10: PWM4 is forced to 0.

11: PWM4 is forced to 1.

PWM3 output.

00: PWM mode 1.

PWM3 is 0 when TC<MR2 during Up-counting period.

01: PWM mode 2.

PWM3 is 1 when TC<MR3 during Up-counting period.

10: PWM3 is forced to 0.

11: PWM3 is forced to 1.

PWM2 output.

00: PWM mode 1.

PWM2 is 0 when TC<MR2 during Up-counting period.

01: PWM mode 2.

PWM2 is 1 when TC<MR2 during Up-counting period.

10: PWM2 is forced to 0.

11: PWM2 is forced to 1.

PWM1 output.

00: PWM mode 1.

Loading...

Loading...