Maintenance—492/492P Service Vol. 1 (SN B030000 & up)

Power-Up Self-Test Mode

The microcomputer enters a self-test mode when the in

strument is turned on if this mode is selected (Fig. 4-24). In

this mode the instrument does not operate normally. The

microcomputer performs the following steps, stopping the

test to indicate the source of any problem found by blinking

an LED on the Processor board.

Addresses are specified as hexadecimal numbers in this

description.

Step 1. At power-up, the microcomputer vectors to the

self-test in the ROM at the top of address space U2028 on

the Memory board. The microcomputer first verifies the

checksum of U2028. If the routine for this step runs, but

does not obtain the correct checksum for the ROM, the rou

tine halts and blinks the ROM 17 LED, DS1044.

This step uses only U2028 and no other memory; so if

the test does not blink the LED and does not proceed to

step 2, U2028 is probably the culprit. Consider first, howev

er, that the correct ROM must be installed, both phases of

the clock on the Processor board must be present, and the

microcomputer system (exclusive of the instrument bus or

GPIB) must be operating correctly. If in doubt about the

6800 microprocessor, its bus, or the microcomputer bus,

skip to the instructions under Microcomputer Test Mode, to

exercise the microcomputer in a more simple manner.

Step 2. The microcomputer next checks the condition of

RAM. This step does not rely on the RAM being ok to ex

ecute. The procedure is: the microcomputer loads the bit

pattern 01010101 into a RAM location, reads the location,

and compares what is returned to what was stored. The

microcomputer then repeats this test with the pattern

10101010.

The microcomputer attempts to test all RAM addresses.

If it finds an error on the Memory board, it stops the test and

pulses the RAM LED, DS1042—once for an error in U2035,

twice for an error in U2032, and three times for an error in

both RAM IC’s; these IC’s are on the Memory board. If the

microcomputer finds an error on the GPIB board, it pulses

the LED 7, 8, or 9 times in a similar manner for low

RAM—U1046 and U1037—or 9, 10, or 11 times for high

RAM—U1042 and U1032. The microcomputer continues to

repeat the number of pulses after an error is found.

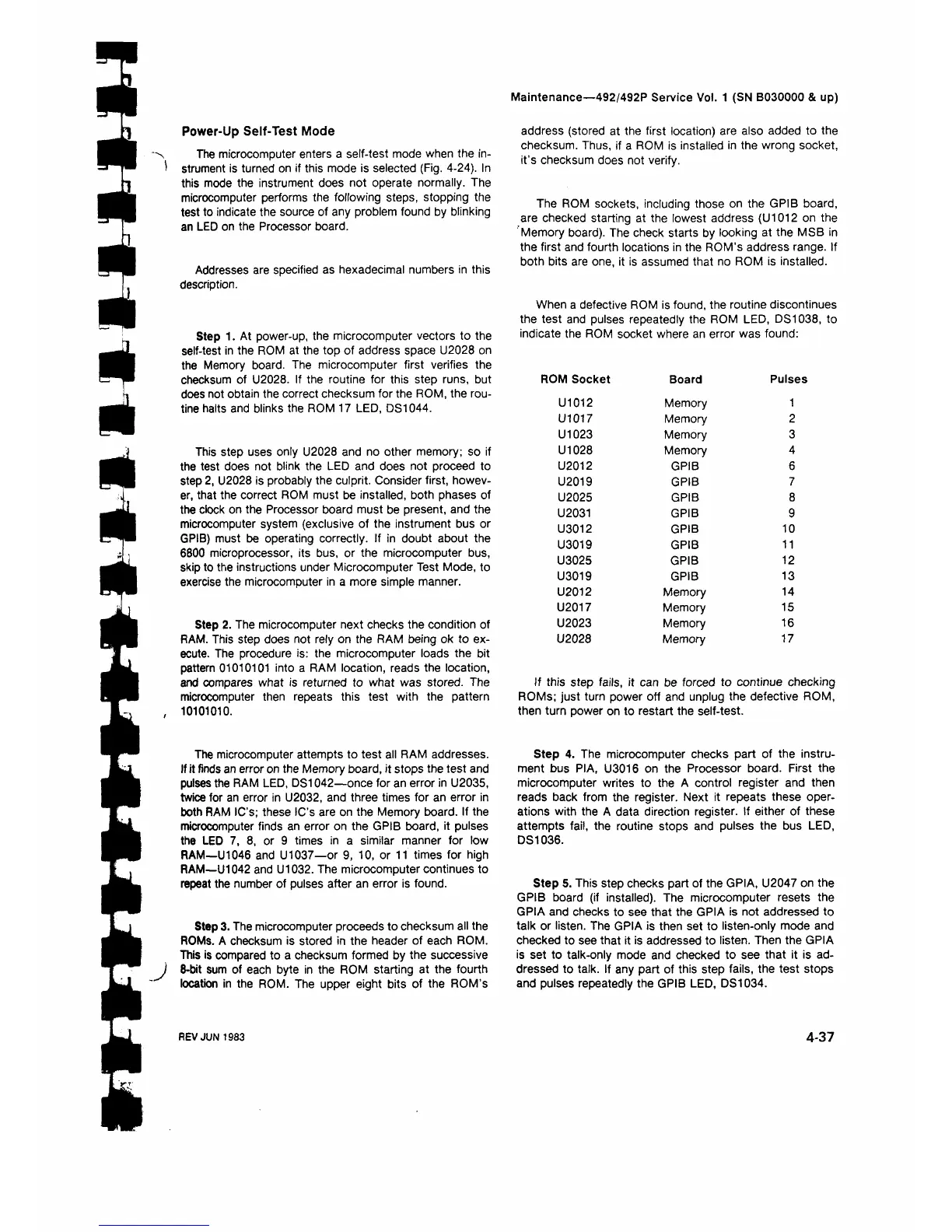

Step 3. The microcomputer proceeds to checksum all the

ROMs. A checksum is stored in the header of each ROM.

This is compared to a checksum formed by the successive

8-bit sum of each byte in the ROM starting at the fourth

location in the ROM. The upper eight bits of the ROM’s

address (stored at the first location) are also added to the

checksum. Thus, if a ROM is installed in the wrong socket,

it's checksum does not verify.

The ROM sockets, including those on the GPIB board,

are checked starting at the lowest address (U1012 on the

Memory board). The check starts by looking at the MSB in

the first and fourth locations in the ROM’s address range. If

both bits are one, it is assumed that no ROM is installed.

When a defective ROM is found, the routine discontinues

the test and pulses repeatedly the ROM LED, DS1038, to

indicate the ROM socket where an error was found:

ROM Socket Board

Pulses

U1012

Memory

1

U1017

Memory

2

U1023 Memory

3

U1028 Memory

4

U2012

GPIB 6

U2019

GPIB 7

U2025

GPIB 8

U2031

GPIB

9

U3012 GPIB 10

U3019 GPIB

11

U3025 GPIB

12

U3019 GPIB

13

U2012 Memory 14

U2017 Memory 15

U2023 Memory 16

U2028

Memory

17

If this step fails, it can be forced to continue checking

ROMs; just turn power off and unplug the defective ROM,

then turn power on to restart the self-test.

Step 4. The microcomputer checks part of the instru

ment bus PIA, U3016 on the Processor board. First the

microcomputer writes to the A control register and then

reads back from the register. Next it repeats these oper

ations with the A data direction register. If either of these

attempts fail, the routine stops and pulses the bus LED,

DS1036.

Step 5. This step checks part of the GPIA, U2047 on the

GPIB board (if installed). The microcomputer resets the

GPIA and checks to see that the GPIA is not addressed to

talk or listen. The GPIA is then set to listen-only mode and

checked to see that it is addressed to listen. Then the GPIA

is set to talk-only mode and checked to see that it is ad

dressed to talk. If any part of this step fails, the test stops

and pulses repeatedly the GPIB LED, DS1034.

REV JUN 1983

4-37

Loading...

Loading...