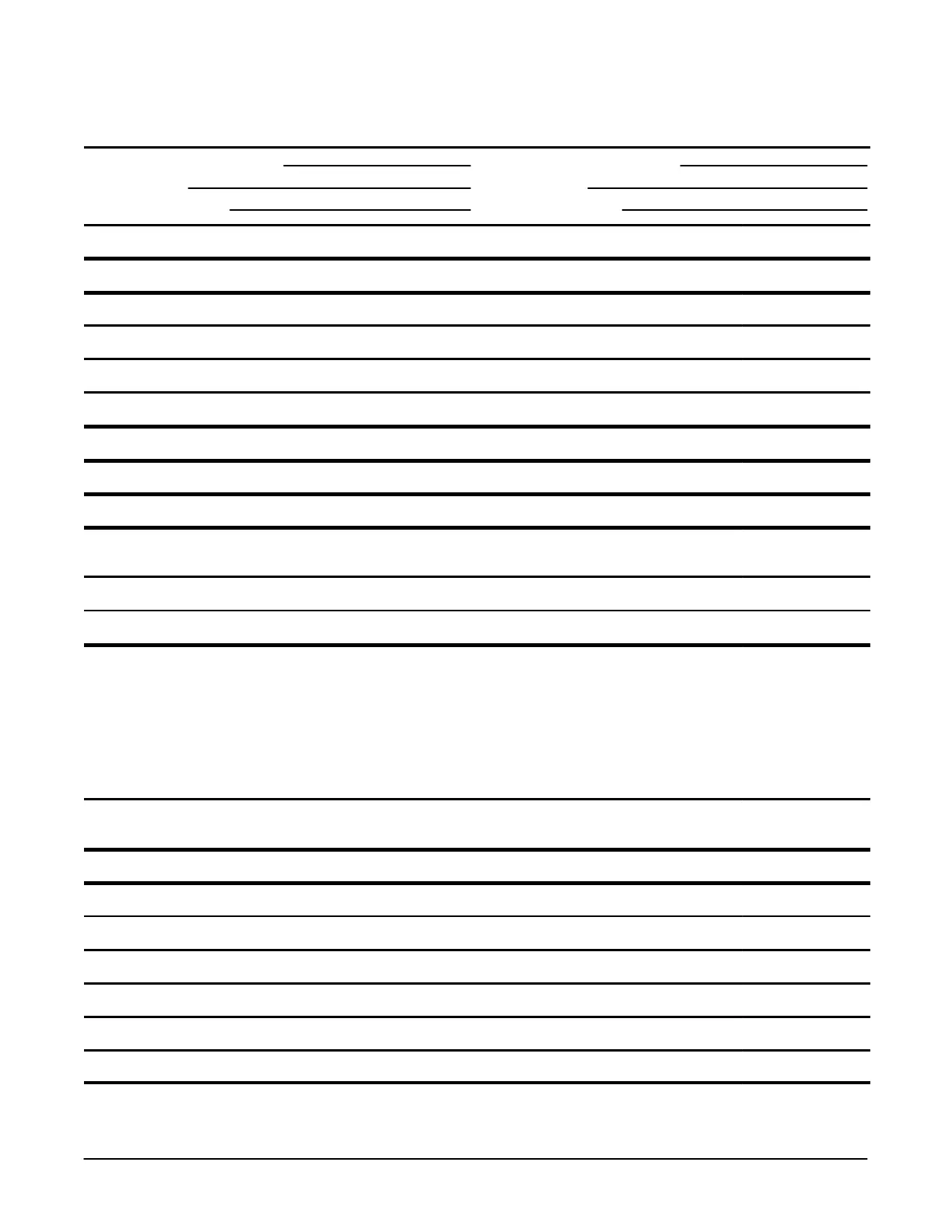

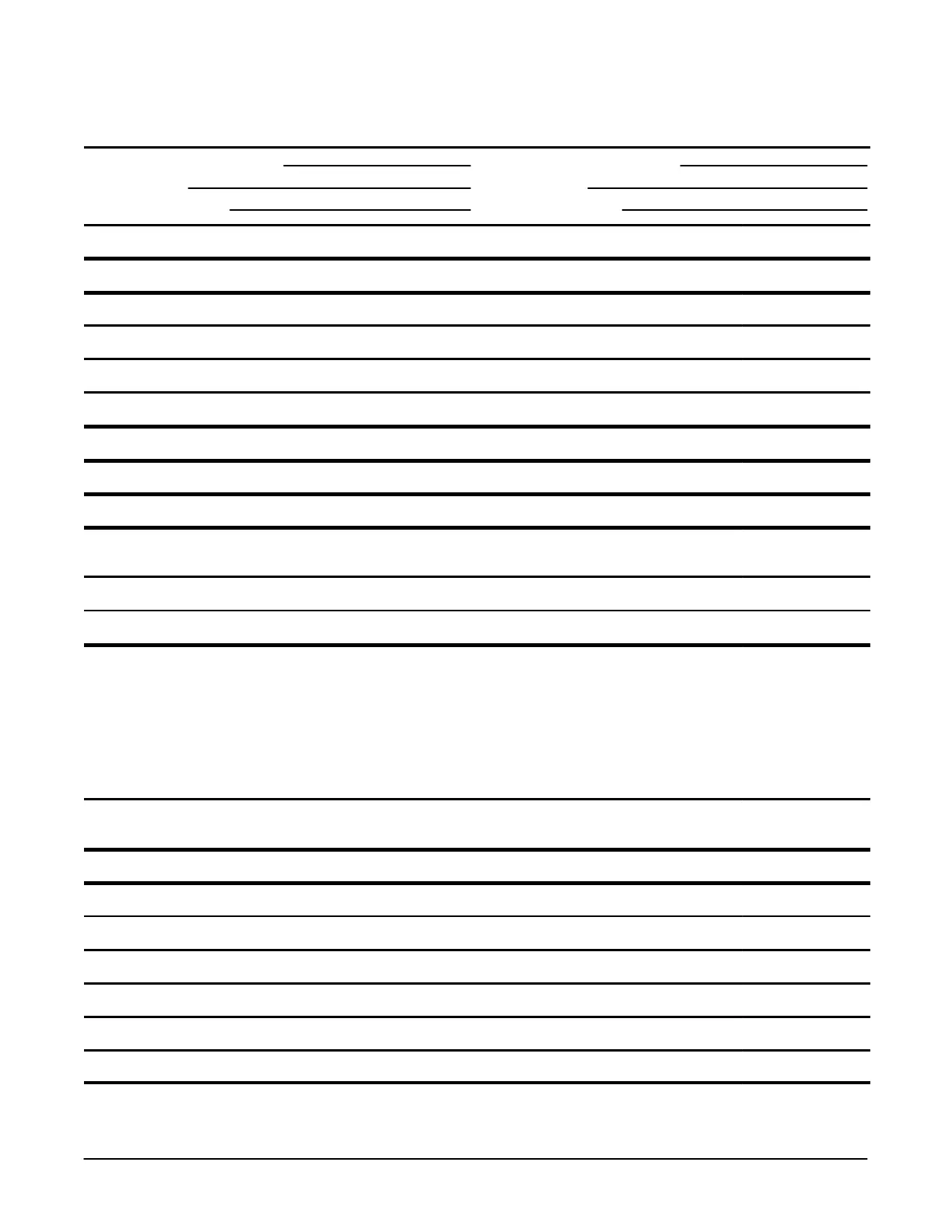

Performance Tests

TDS 520A, 524A, 540A, & 544A Service Manual

4Ć21

TDS 500A Test Record (Cont.)

Instrument Serial Number: Certificate Number:

Temperature: RH %:

Date of Calibration: Technician:

Performance Test MaximumOutgoingIncomingMinimum

Analog Bandwidth

CH1 100 mV 424 mV __________ __________ N/A

CH2 100 mV 424 mV __________ __________ N/A

CH3 100 mV 424 mV __________ __________ N/A

CH4 100 mV 424 mV __________ __________ N/A

Delay Between Channels

Delay Between Channels N/A __________ __________ 250 ps

Time Base System

Long Term Sample Rate/

Delay Time @ 500 ns/10 ms -2.5 Div __________ __________ +2.5 Div

Delta Time@5ns(100 MHz) 19.760 ns __________ __________ 20.240 ns

Trigger System Accuracy

PulseĆGlitch or PulseĆWIdth,

Hor. scale ≤ 1 ms

Lower Limit

Upper Limit

PulseĆGlitch or PulseĆWIdth,

Hor. scale > 1 ms

Lower Limit

Upper Limit

2.5 ns

2.5 ns

1 ms

1 ms

__________

__________

__________

__________

__________

__________

__________

__________

7.5 ns

7.5 ns

3 ms

3 ms

Main Trigger, DC Coupled)

Delayed Trigger, DC Coupled)

9.940 V

9.940 V

__________

__________

__________

___________

10.060 V

10.060 V

Output Signal Checks

MAIN TRIGGER OUTPUT, 1 M W High ≥ 2.5 V __________ __________ Low ≤ 0.7 V

MAIN TRIGGER OUTPUT, 50 W High ≥ 1.0 V __________ __________ Low ≤ 0.25 V

DELAYED TRIGGER OUTPUT, 50 W High ≥ 1.0 V __________ __________ Low ≤ 0.25 V

DELAYED TRIGGER OUTPUT, 1 M W High ≥ 2.5 V __________ __________ Low ≤ 0.7 V

CH 3 SIGNAL OUTPUT, 1 M W PkĆPk ≥ 90 mV __________ __________ PkĆPk ≤ 110 mV

CH 3 SIGNAL OUTPUT, 50 W PkĆPk ≥ 45 mV __________ __________ PkĆPk ≤ 55 mV

Loading...

Loading...