Telink TLSR8232 BLE SDK Developer Handbook

AN-19112700-E1 179 Ver.1.0.0

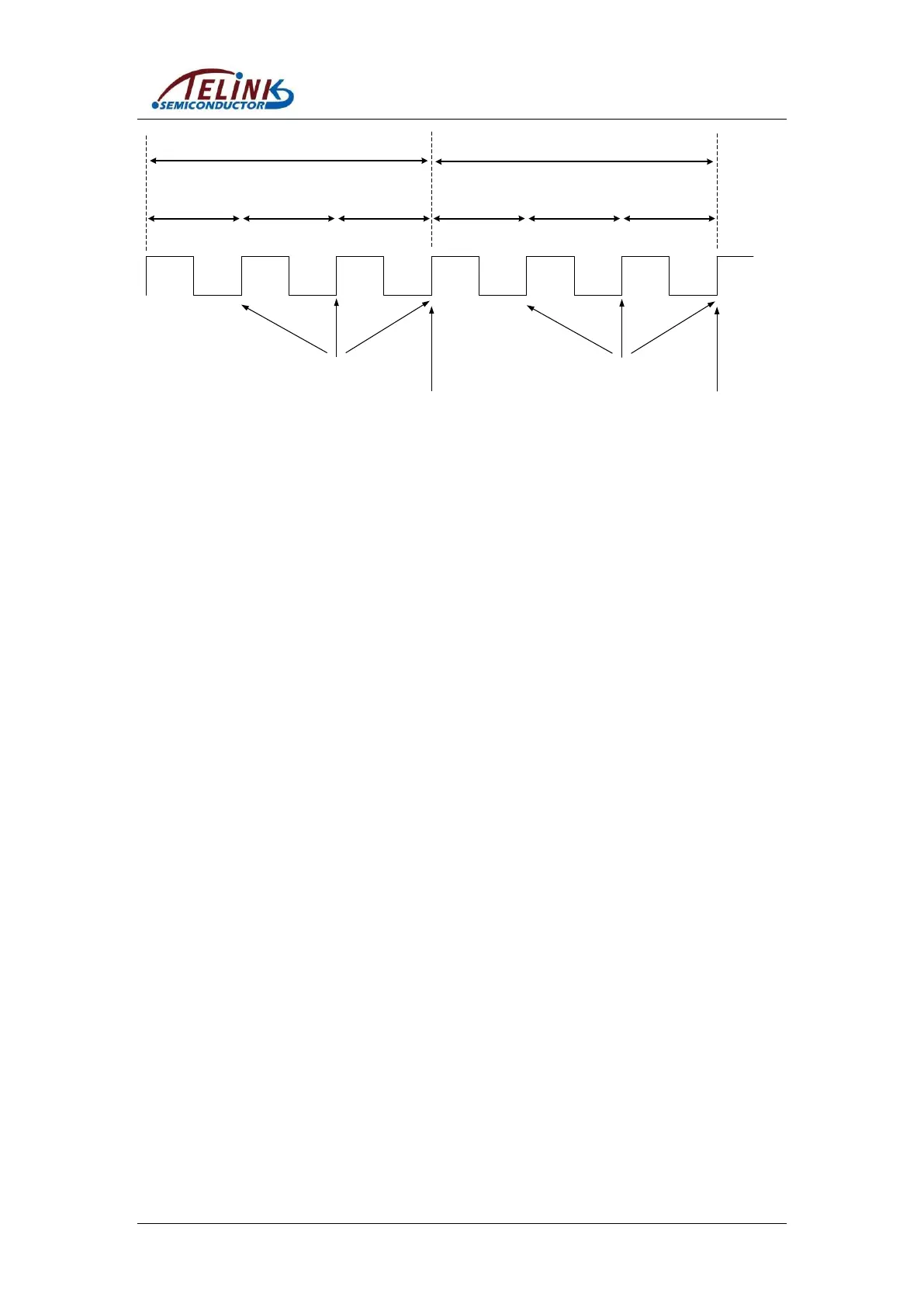

Signal Frame Signal Frame Signal Frame Signal Frame Signal Frame Signal Frame

IRQ_PWM0_FRAME

IRQ_PWM0_PNUM

IRQ_PWM0_FRAME

IRQ_PWM0_PNUM

IR task

(pulse number = 3)

IR task

(pulse number = 3)

Figure 10-2 PWM interrupt

1) IRQ_PWMn_FRAME(n=0,1,2,3,4,5) for PWM0~PWM5: After each signal frame,

PWM#n (n=0~5) will generate a frame-done IRQ (Interrupt Request) signal

“IRQ_PWMn_FRAME”.

As shown in the figure above, six frame-done IRQ signal are generated at the end of

each PWM0 Signal Frame.

2) IRQ_PWM0_PNUM: In Counting mode and IR mode, PWM0 will generate a Pnum

IRQ signal “IRQ_PWM0_PNUM” after completing a group of Signal Frames (pulse

number is determined by the API pwm_set_pulse_num).

As shown in the figure above, PWM0 will generate a Pnum IRQ signal at the end of

a pulse group containing three Signal Frames.

3) IRQ_PWM0_IR_DMA_FIFO_DONE

In IR DMA FIFO mode, PWM0 will generate an IR waveform send done IRQ signal

“IRQ_PWM0_IR_DMA_FIFO_DONE”, after all PWM waveforms configured in DMA

are sent.

As described above, IRQ request won’t trigger interrupt response unless all of its related

“mask” bits are enabled. Taking “FLD_IRQ_PWM0_PNUM” for an example, three “mask”

bits need to be enabled.

1) Enable “mask” of FLD_IRQ_PWM0_PNUM, i.e. core_7b0:

reg_pwm_irq_mask |= FLD_IRQ_PWM0_PNUM;

Generally, to avoid false triggering of interrupt response, previous “status” needs to

cleared before enabling “mask”.

reg_pwm_irq_sta = FLD_IRQ_PWM0_PNUM;

2) Enable PWM “mask” in MCU system interrupt, i.e. core_640 BIT<14>.

#define reg_irq_mask REG_ADDR32(0x640)

enum{

……

FLD_IRQ_SW_PWM_EN = BIT(14), //irq_software | irq_pwm

……

Loading...

Loading...