Copyright © 2015 Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. All other brands are property of their respective owners.

Avnet Electronics Marketing 14 of 28 Rev D 24 Apr 2015

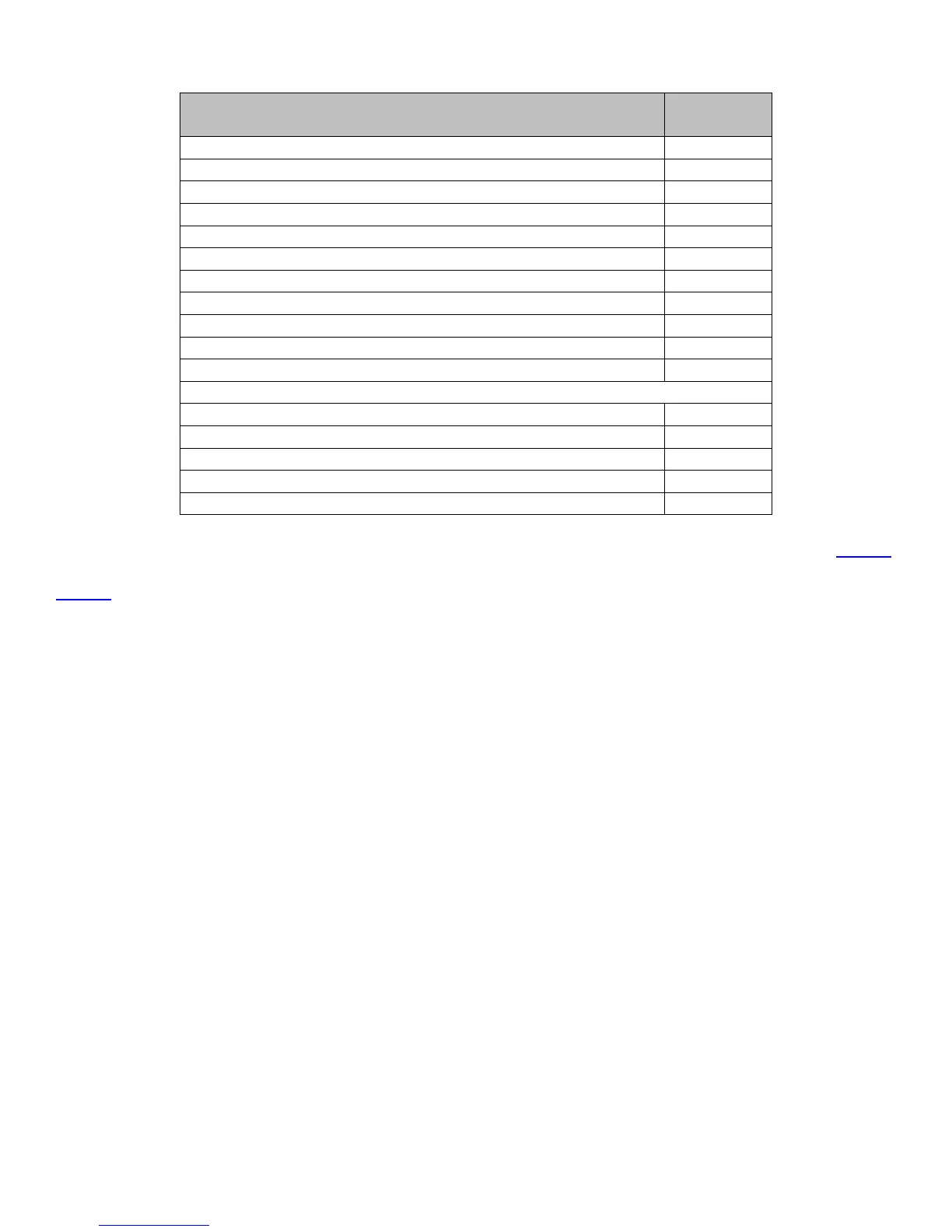

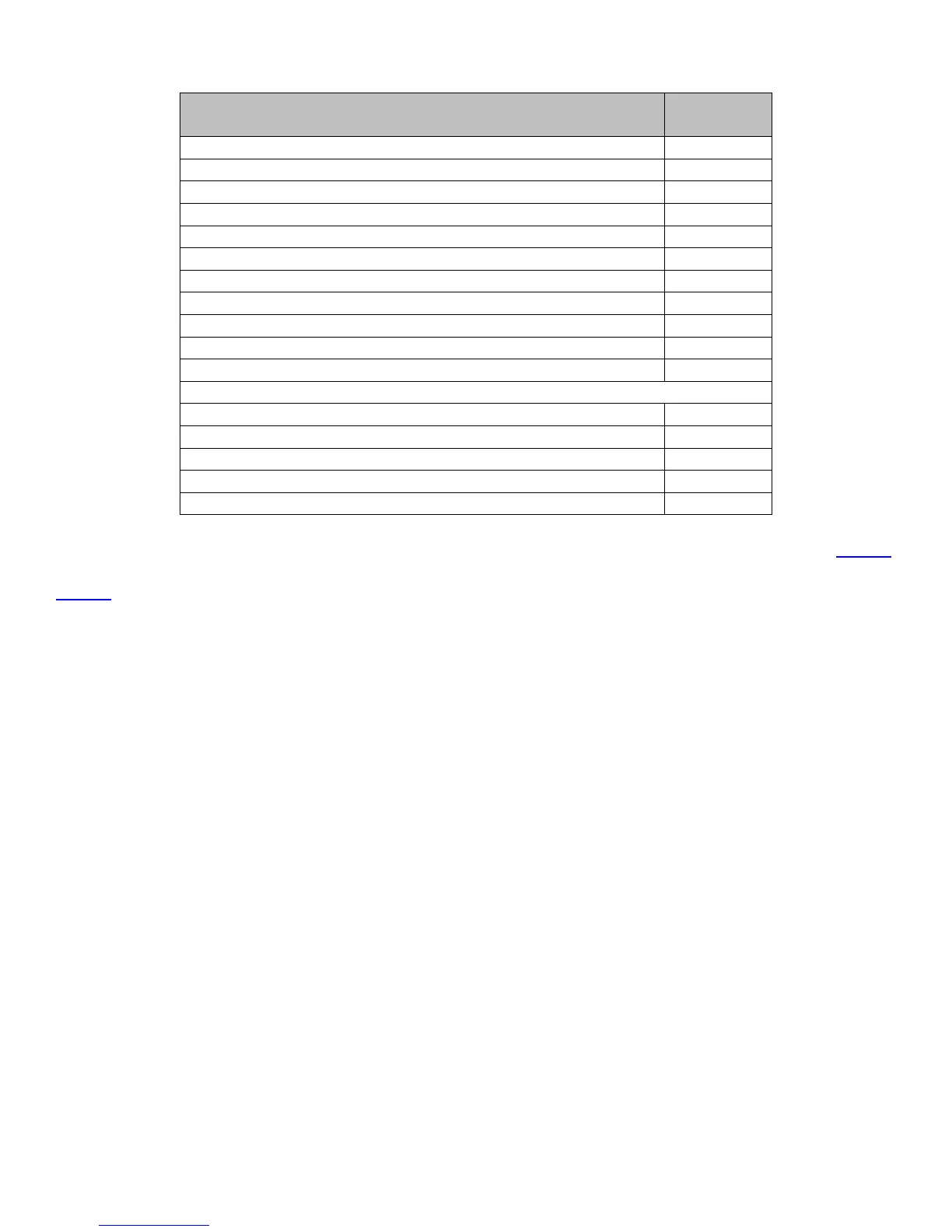

Table 5 – LPDDR Timing Parameters

MT47H16M16BG-5E: Timing Parameters Time (ps)

or Number

Load Mode Register time (TMRD) 2 tCK

Write Recovery time (TWR) 15000

Write-to-Read Command Delay (TWTR) 10000

Delay between ACT and PRE Commands (TRAS) 40000

Delay after ACT before another ACT (TRC) 55000

Delay after AUTOREFRESH Command (TRFC) 75000

Delay after ACT before READ/WRITE (TRCD) 15000

Delay after ACT before another row ACT (TRRD) 10000

Delay after PRECHARGE Command (TRP) 15000

Refresh Command Interval (TREFC) 70000000

Avg. Refresh Period (TREFI) 7800000

Memory Data Width (DWIDTH) (2 devices) 32

Row Address Width (AWIDTH) 13

Column Address Width (COL_AWIDTH) 9

Bank Address Width (BANK_AWIDTH) 2

Memory Range (64 MB total) 0x3FFFFFF

The layout guidelines for Spartan-6 MCB designs, as detailed in Spartan-6 FPGA Memory Controller, UG388,

were followed in the design of this board. The pinout specified in the Spartan-6 Packaging & Pinout Guide,

UG385 for the XC6SLX9-CSG324 was followed.

Loading...

Loading...