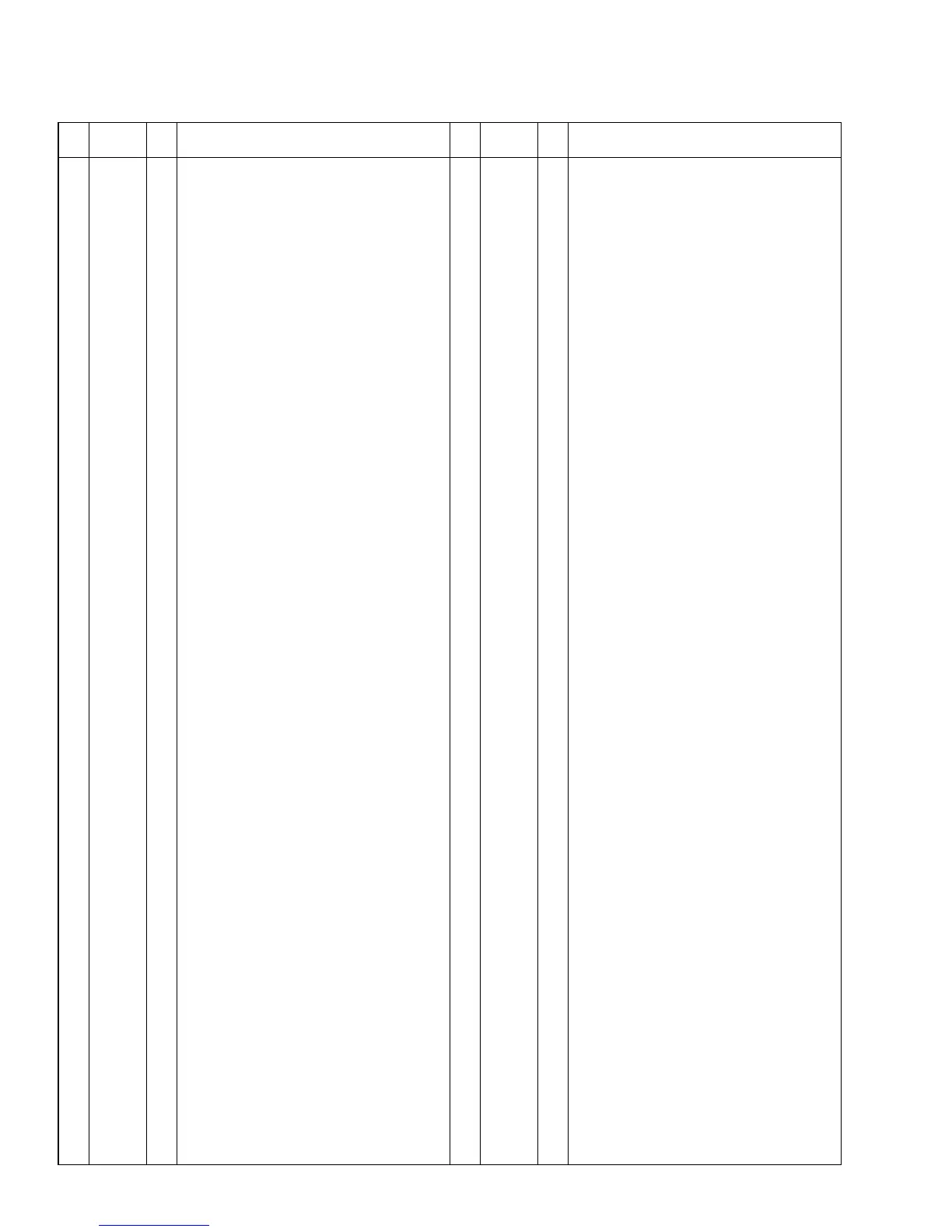

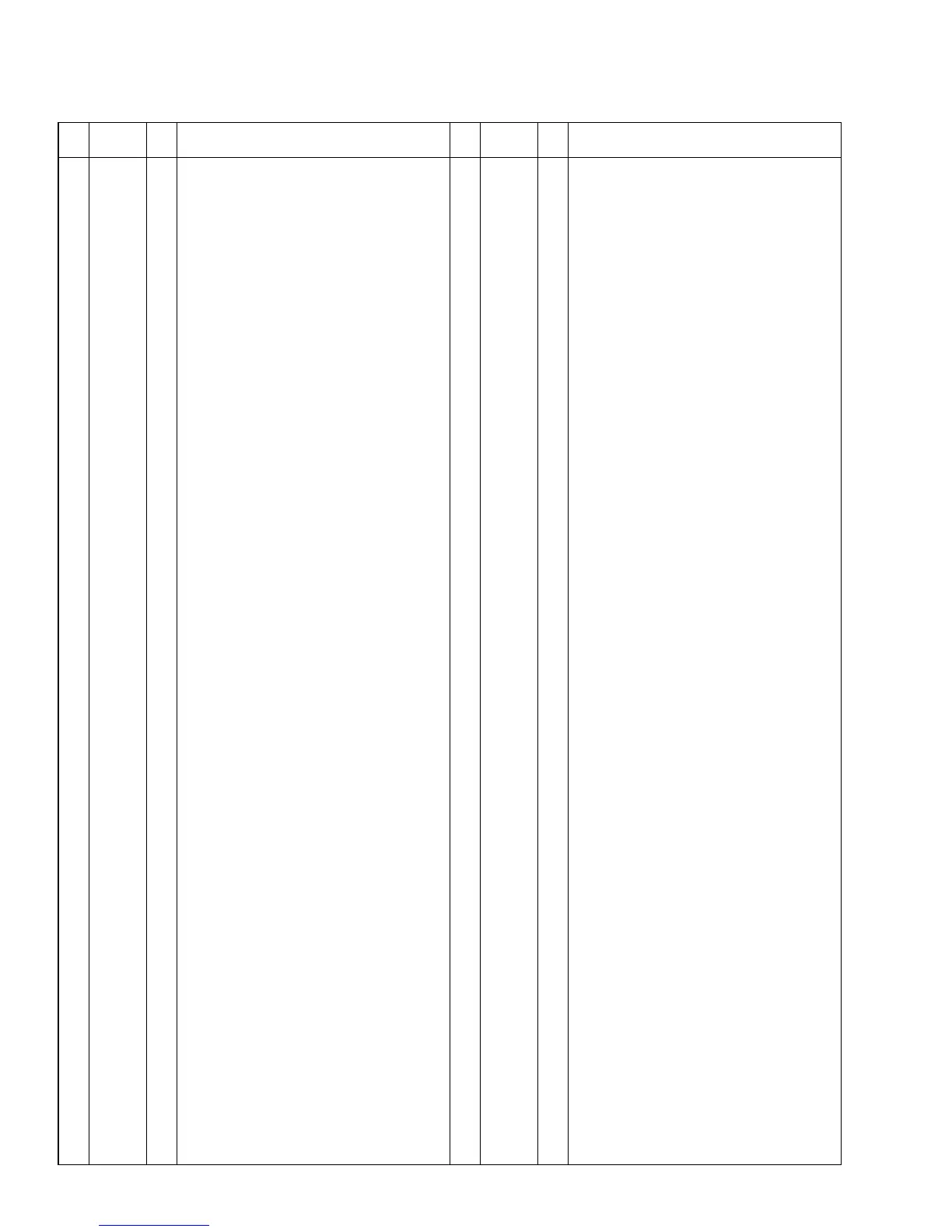

24

O1X

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

135

IRQ# mLAN

I/O In 8415 mode, interrupt request output from

PH1 block to microprocessor

136 CE8# TRI MPU CE8 signal

137 CPU D0 I/O MPU data bus

138 CPU D1 I/O MPU data bus

139 CPU D2 I/O MPU data bus

140 CPU D3 I/O MPU data bus

141 VSS Ground terminal

142 CPU D4 I/O MPU data bus

143 CPU D5 I/O MPU data bus

144 CPU D6 I/O MPU data bus

145 CPU D7 I/O MPU data bus

146 CPU D8 I/O MPU data bus

147 CPU D9 I/O MPU data bus

148 VDD Power terminal

149 CPU D10 I/O MPU data bus

150 CPU D11 I/O MPU data bus

151 CPU D12 I/O MPU data bus

152 CPU D13 I/O MPU data bus

153 CPU D14 I/O MPU data bus

154 CPU D15 I/O MPU data bus

155 VSS Ground terminal

156 CE4# TRI MPU CE4 signal

157 MISC0 I/O General purpose input/output terminal

158 MISC1 I/O General purpose input/output terminal

159 MISC2 I/O General purpose input/output terminal

160 CE10EX# I/O MPU CE10EX signal

161 VDD Power terminal

162 NMI# I MPU NMI signal

163 TST I Test terminal

164 CPU A19 I/O MPU address bus

165 CPU A18 I/O MPU address bus

166 CPU A17 I/O MPU address bus

167 CPU A16 I/O MPU address bus

168 CPU A15 I/O MPU address bus

169 VSS Ground terminal

170 CPU A14 I/O MPU address bus

171 CPU A13 I/O MPU address bus

172 CPU A12 I/O MPU address bus

173 CPU A11 I/O MPU address bus

174 CPU A10 I/O MPU address bus

175 CPU A9 I/O MPU address bus

176 VDD Power terminal

177 CPU A8 I/O MPU address bus

178 CPU A7 I/O MPU address bus

179 CPU A6 I/O MPU address bus

180 CPU A5 I/O MPU address bus

181 CPU A4 I/O MPU address bus

182 CPU A23 I/O MPU address bus

183 VSS Ground terminal

184 CPU A3 I/O MPU address bus

185 CPU A22 I/O MPU address bus

186 CPU A2 I/O MPU address bus

187 CPU A21 I/O MPU address bus

188 CPU A1 I/O MPU address bus

189 CPU A20 I/O MPU address bus

190 CPU A0 I/O MPU address bus

191 EA10MD0 I MPU area 10 boot mode select signal

192 EA10MD1 I MPU area 10 boot mode select signal

193 EA10MD2 I MPU area 10 boot mode select signal

194 VDD Power terminal

195 DSIO I/O Serial input/output terminal for debugging

196

P14/DCLK

I/O General purpose port 14/serial input/output

terminal for debugging

197

P13/DPC0

I/O General purpose port 13/serial input/output

terminal for debugging

198

P12/DST2

I/O General purpose port 12/serial input/output

terminal for debugging

199

P11/DST1

I/O General purpose port 11/serial input/output

terminal for debugging

200

P10/DST0

I/O General purpose port 10/serial input/output

terminal for debugging

201 VSS Ground terminal

202 PLLS0 I MPU PLL setting terminal

203 PLLS1 I MPU PLL setting terminal

204

TEST6 TVEP

I Test terminal

205

P00/SRXD1

I/O General purpose port 00/serial I/F

206

P01/STXD1

I/O General purpose port 01/serial I/F

207

P02/SCLK1#

I/O General purpose port 02/serial I/F

208

P03/SRDY1#

I/O General purpose port 03/serial I/F

209

P04/SRXD2

I/O General purpose port 04/serial I/F

210

P05/STXD2

I/O General purpose port 05/serial I/F

211

P06/SCLK2#

I/O General purpose port 06/serial I/F

212

P07/SRDY2#

I/O General purpose port 07/serial I/F

213 INT3# O LINK section interrupt signal

214 GPIO[0] I/O

LINK section general purpose input/output signal

215 GPIO[1] I/O

LINK section general purpose input/output signal

216 TXE I/O Enable output (SLV:L), input (SLV:H)for multi

chip transmission

217 SWCK I/O Word clock output (SLV:L), input (SLV:H) for

multi chip transmission

218 X2SPD# I Double speed mode

219 VDD Power terminal

220 LINKON I LinkOn input signal

221 DIRECT I PHY I/F direct select signal

222

CS# LINK

I LINK section chip select signal

223

INT1# LINK

I/O In 8415 mode, LINK section interrupt signal 1

and in standalone mode, MPU P26 signal

224

INT2# LINK

I/O In 8415 mode, LINK section interrupt signal 2

and in standalone mode, MPU P27 signal

225 VSS Ground terminal

226

BUSMASTER

I MPU bus master

227

CYCLEOUT

I/O

In normal mode: Iso cycle output. When only PH1

at work: Isochronous cycle OUT signal input

228 VDD Power terminal

229 IRERR# I/O In normal mode: Isochronous packet error flag.

When only PH1 at work: Isochronous packet

error flag input

230 IRCV# I/O In normal mode: Isochronous packet reception

enable. When only PH1 at work: Isochronous

reception enable input

231 IRX# I/O In normal mode: Isochronous reception data

enable. When only PH1 at work: Isochronous

reception data enable input

232 ICLK I/O In normal mode: Isochronous bus master clock.

When only PH1 at work: Isochronous master

clock input

233 VSS Ground terminal

234 IDATA15 I/O Bus exclusively for Isochronous data access

235 IDATA14 I/O Bus exclusively for Isochronous data access

236 IDATA13 I/O Bus exclusively for Isochronous data access

237 IDATA12 I/O Bus exclusively for Isochronous data access

238 IDATA11 I/O Bus exclusively for Isochronous data access

239 IDATA10 I/O Bus exclusively for Isochronous data access

240 IDATA9 I/O Bus exclusively for Isochronous data access

241 IDATA8 I/O Bus exclusively for Isochronous data access

242 VDD Power terminal

243 IDATA7 I/O Bus exclusively for Isochronous data access

244 IDATA6 I/O Bus exclusively for Isochronous data access

245 IDATA5 I/O Bus exclusively for Isochronous data access

246 IDATA4 I/O Bus exclusively for Isochronous data access

247 IDATA3 I/O Bus exclusively for Isochronous data access

248 IDATA2 I/O Bus exclusively for Isochronous data access

249 IDATA1 I/O Bus exclusively for Isochronous data access

250 IDATA0 I/O Bus exclusively for Isochronous data access

251 VSS Ground terminal

252 ITX# I/O In normal mode: Isochronous transmission data

enable. When only PH1 at work: Isochronous

transmission data enable input

253 IEOP# I/O In normal mode: if other NC1 or PH2 is cascade

connected: Isochronous transmission packet

end. When only PH1 at work: Isochronous

transmission packet end output

254 ITREQ# I/O In normal mode: if other NC1 or PH2 is cascade

connected: Isochronous transmission request.

When only PH1 at work: Isochronous

transmission request output

255 CT I/O

In normal mode: cycle timer enable. When only

PH1 at work: Isochronous cycle timer enable input

256 ICS I/O

In normal mode: Isochronous Cycle Start Packet

transmission/reception timing output. When only PH1

at work: isochronous cycle start signal input

Loading...

Loading...