CP1484, CP1485, CP1486, CP3484, CP3485, CP3486

9Data sheet V 1.00

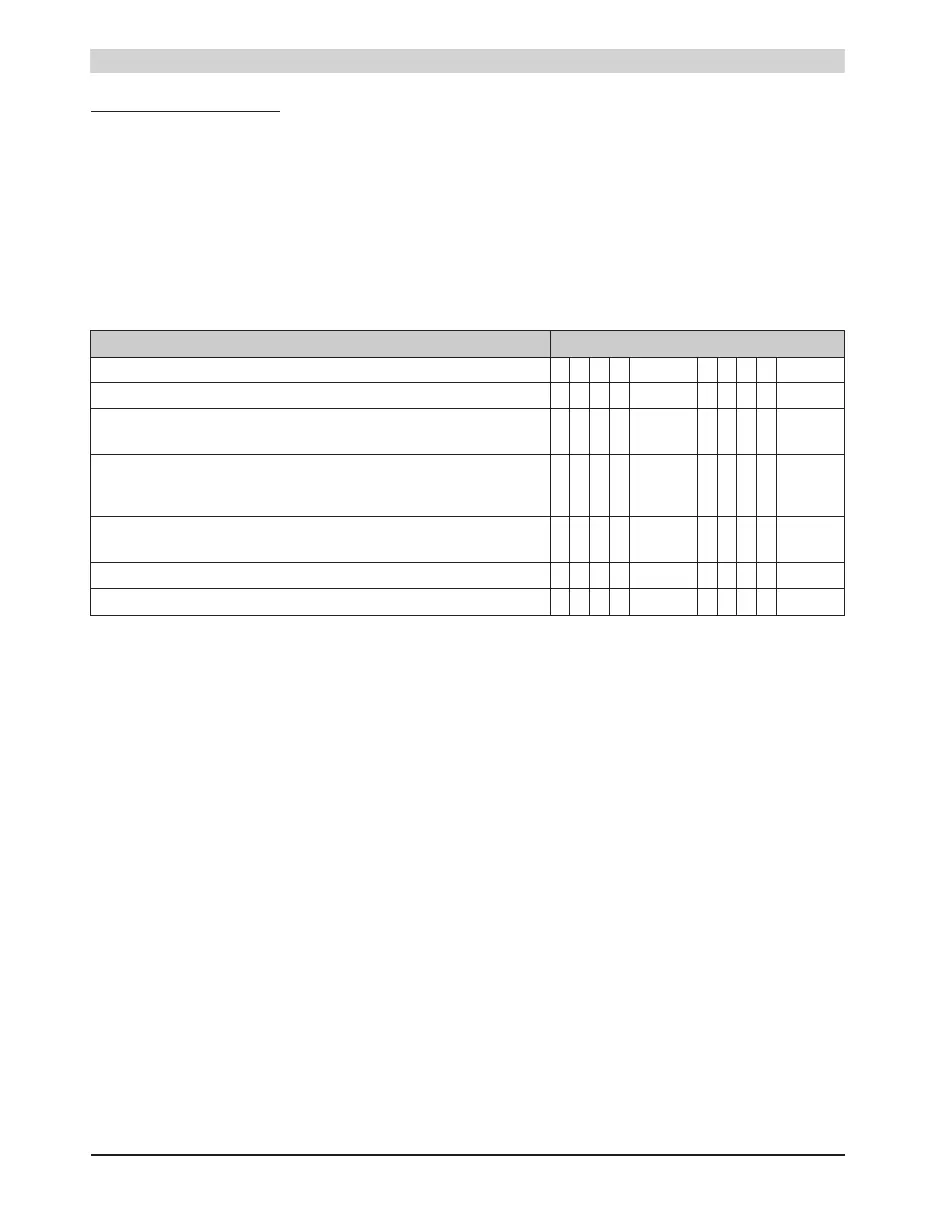

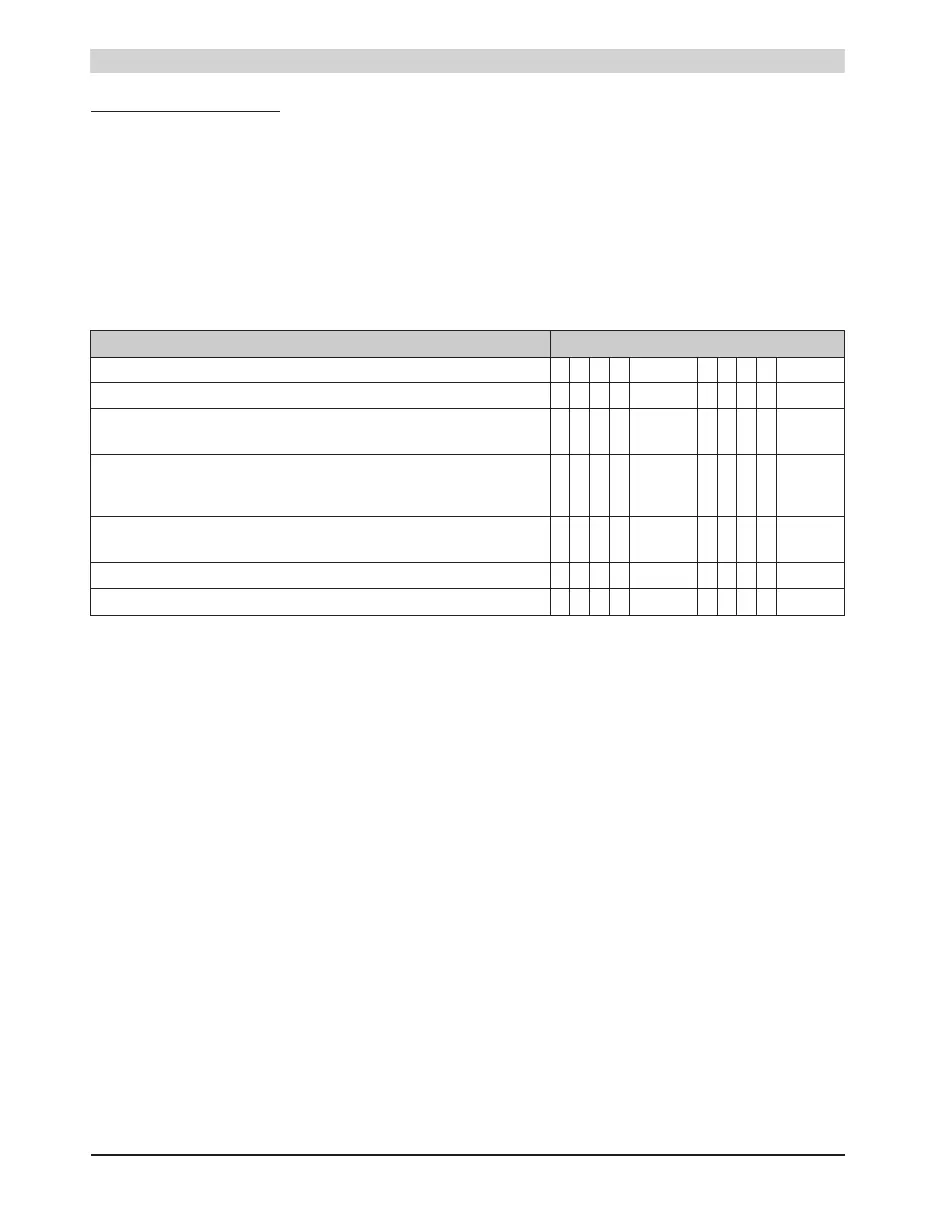

System halt error codes

Incorrect configuration or defective hardware can cause a system halt error.

The error is displayed via the red error LED using four switch-on phases. The switch-on phases

are either 150 ms or 600 ms long. Error code outputs are repeated cyclically after 2 seconds has

passed.

Legend: • ... 150 ms

− ... 600 ms

Pause ... 2 s delay

Error description Error code displayed by red status LED

Stack overflow

••••

Pause

••••

Pause

RAM Error

•••−

Pause

•••−

Pause

Undefined address:

Access to a non-existent address

••−•

Pause

••−•

Pause

Instruction fetch memory abort:

Invalid memory access during fetch instruction (e. g. UINT access of an uneven

address).

••−−

Pause

••−−

Pause

Data access memory abort:

Invalid memory access during data access (e. g. UINT access of an odd address).

•−• •

Pause

•−••

Pause

Error programming the FPGA

• −−•

Pause

•−−•

Pause

Invalid station number (e. g. $FE or $FF)

• −−−

Pause

•−−−

Pause

Table 8: X20 CPUs status/error LED as error LED - system halt error codes

Loading...

Loading...