Using High-Speed Counter Instructions

12–9

When

a high preset is reached, no counts are lost.

• Hardware and instruction accumulators are reset.

• Instruction high preset is loaded to the hardware high preset.

• If the DN bit is not set, the DN bit is set. The IH bit is also set and the IL, IV,

and IN bits are reset.

• If the DN bit is already set, the OV bit is set. The IV bit is also set and the IL,

IV and IN bits are reset.

• High-speed counter interrupt file (program file 4) is executed if the interrupt is

enabled.

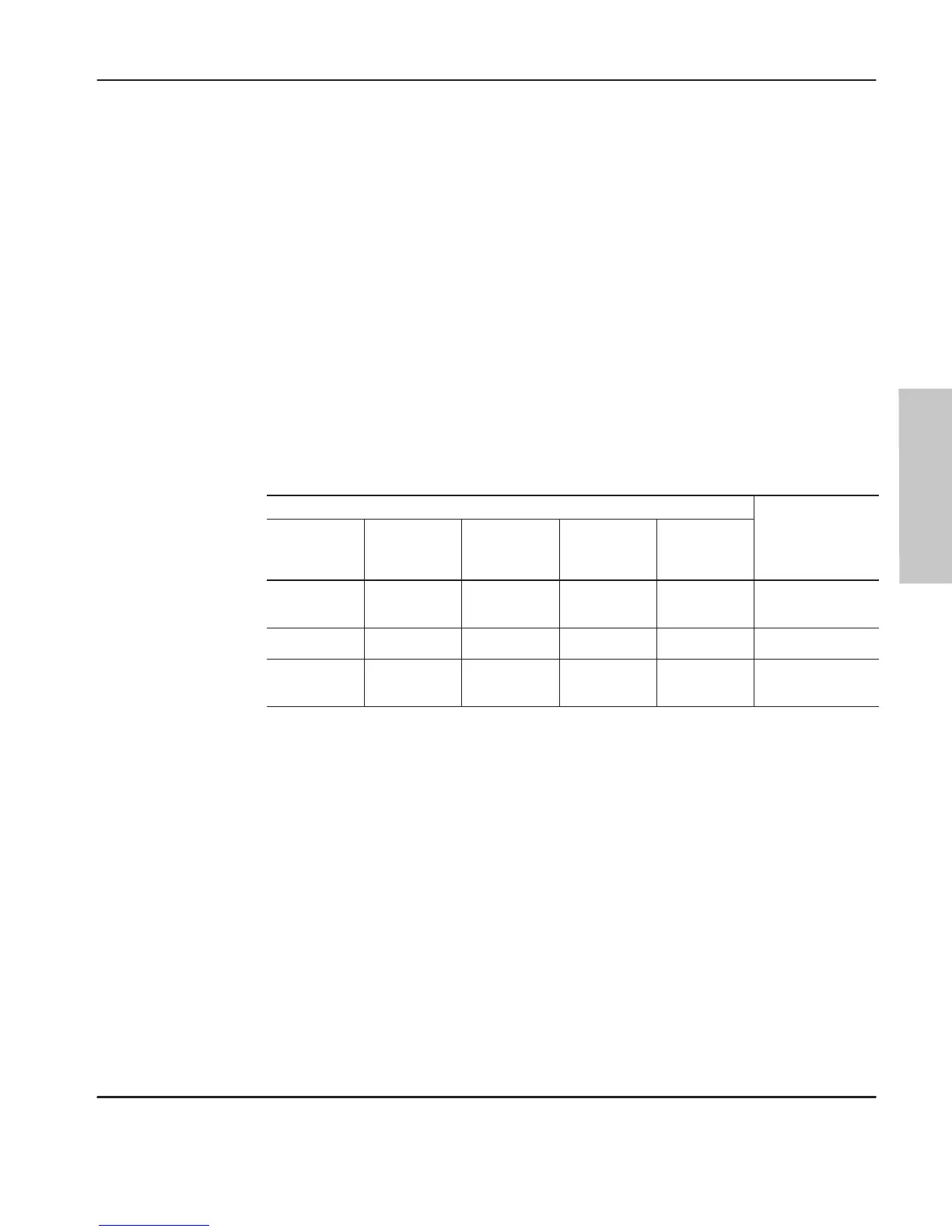

The following tables summarize what the input state must be for the corresponding

high-speed counter action to occur:

Up Counter

Input State

Input Count

(I/O)

Input

Direction

(I/1)

Input Reset

(I/2)

Input Hold

(I/3)

HSC Rung

High-Speed

Counter Action

Turning

Off-to-On

NA NA NA True Count Up

NA NA NA NA False Hold Count

Off, On, or

Turning Off

NA

Off, On, or

Turning Off

NA NA Hold Count

NA (Not Applicable)

Programming

efesotomasyon.com - Allen Bradley,Rockwell,plc,servo,drive

Loading...

Loading...