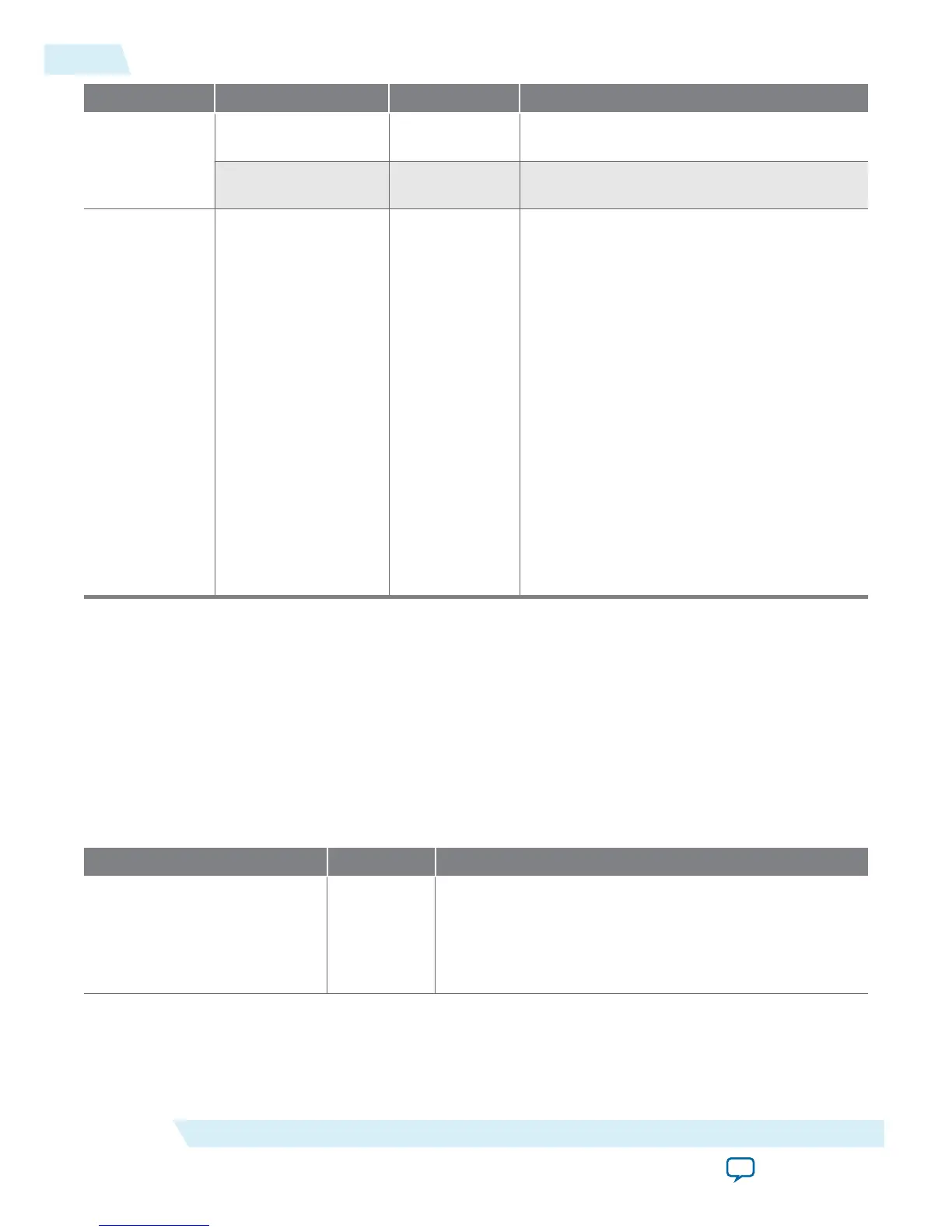

Page Parameter Value Description

EDA

Simulation Libraries — Specifies the libraries for functional

simulation.

Generate netlist On, Off Turn on this option to generate synthesis area

and timing estimation netlist.

Summary — —

Specifies the types of files to be generated. A

gray checkmark indicates a file that is

automatically generated; an unchecked check

box indicates an optional file. Choose from

the following types of files:

• AHDL Include file (<function name>.inc)

• VHDL component declaration file

(<function name>.cmp)

• Quartus II symbol file (<function name>

.bsf)

• Instantiation template file (<function

name>_inst.v or <function name>_

inst.vhd)

• Verilog HDL black box file (<function

name>_bb.v)

If the Generate netlist option is turned on,

the file for that netlist is also available

(<function name>_syn.v).

Related Information

• Programmable Phase Shift on page 2-20

• Dynamic Phase Configuration Implementation on page 4-15

• PLL Reconfiguration on page 2-26

• Dynamic Phase Configuration Implementation on page 4-15

ALTPLL_RECONFIG Ports and Signals

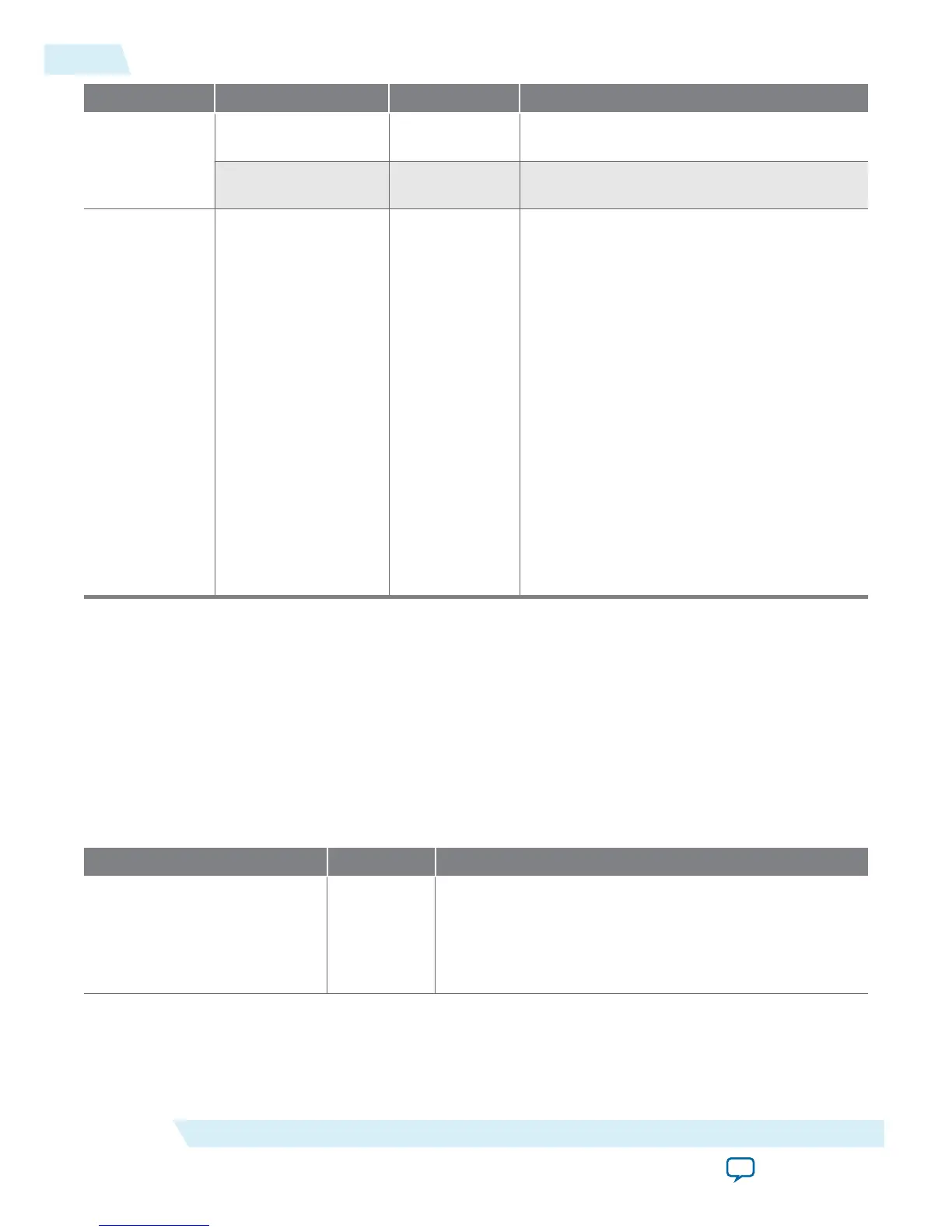

Table 7-2: ALTPLL_RECONFIG Input Ports for MAX 10 Devices

Port Name Condition Description

clock

Required Clock input for loading individual parameters. This signal

also clocks the PLL during reconfiguration.

The clock input port must be connected to a valid clock.

Refer to the MAX 10 Device Datasheet for the clock f

MAX

.

7-2

ALTPLL_RECONFIG Ports and Signals

UG-M10CLKPLL

2015.06.12

Altera Corporation

ALTPLL_RECONFIG IP Core References

Send Feedback

Loading...

Loading...