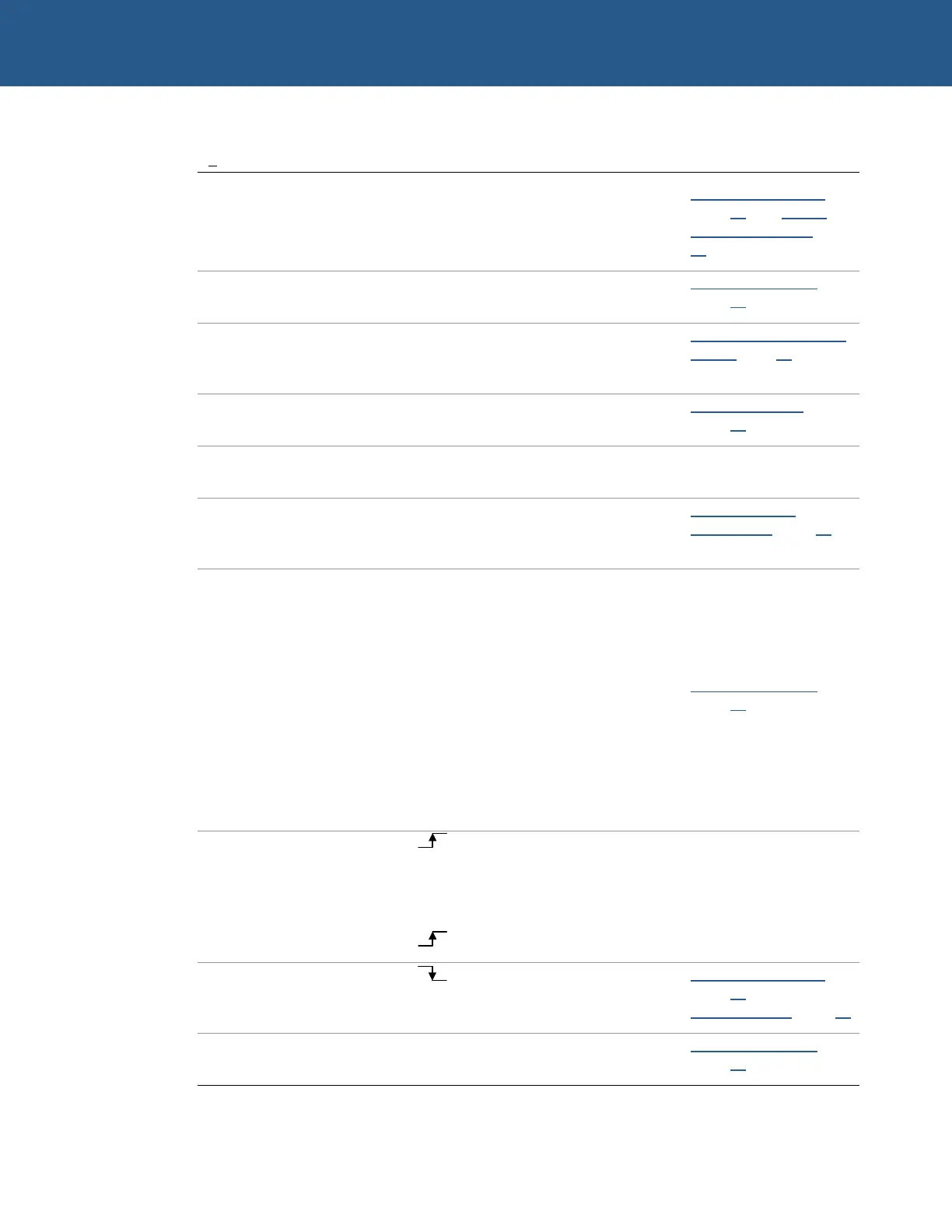

VIPER Detailed hardware description

GPIO

No

AF

Signal Name Dir Active Sleep Function See section…

14 0 FLASH_

STATUS

Input NA Input Bootloader FLASH

Status,

Ready / nBusy

Interrupt assignments

(page 25

) and FLASH

memory/silicon disk

(page

23

)

15 2 CS1 Output Low Hi-Z Chip Select 1 VIPER address map

(page 14

)

16 2 PWM0 Output See

inverter

datasheet

0 Backlight Brightness

On/Off or variable if

PWM

LCD backlight brightness

control

(page 32)

17 2 PWM1 Output NA 0 STN Bias STN BIAS voltage

(page 32

)

18 1 ARDY Input Low Input 10/100 Ethernet PHY

Ready

-

19 0 PSU_nCS_LD Output Low 0 Microprocessor Core

Voltage DAC Chip

Select

Processor power

management

(page 55)

20 0 OUT0

21 0 OUT1

22 0 OUT2

23 0 OUT3

24 0 OUT4

25 0 OUT5

26 0 OUT6

27 0 OUT7

Output

User

Config

0 User Config

General purpose I/O

(page 39

)

28 1 AC97_BITCLK Input Input BITCLK

29 1 AC97_IN Input NA Input SDATA_IN0

30 2 AC97_OUT Output NA 0 SDATA_OUT

31 2 AC97_SYNC Output 0 SYNC

-

32 0 CF_DETECT Input Input CF Detection Interrupt assignments

(page 25

) and

CompactFLASH

(page 24)

33 2 CPLDCS Output Low Hi-Z Chip Select 5 VIPER address map,

(page 14

)

© 2004 Arcom Issue H 18

Loading...

Loading...