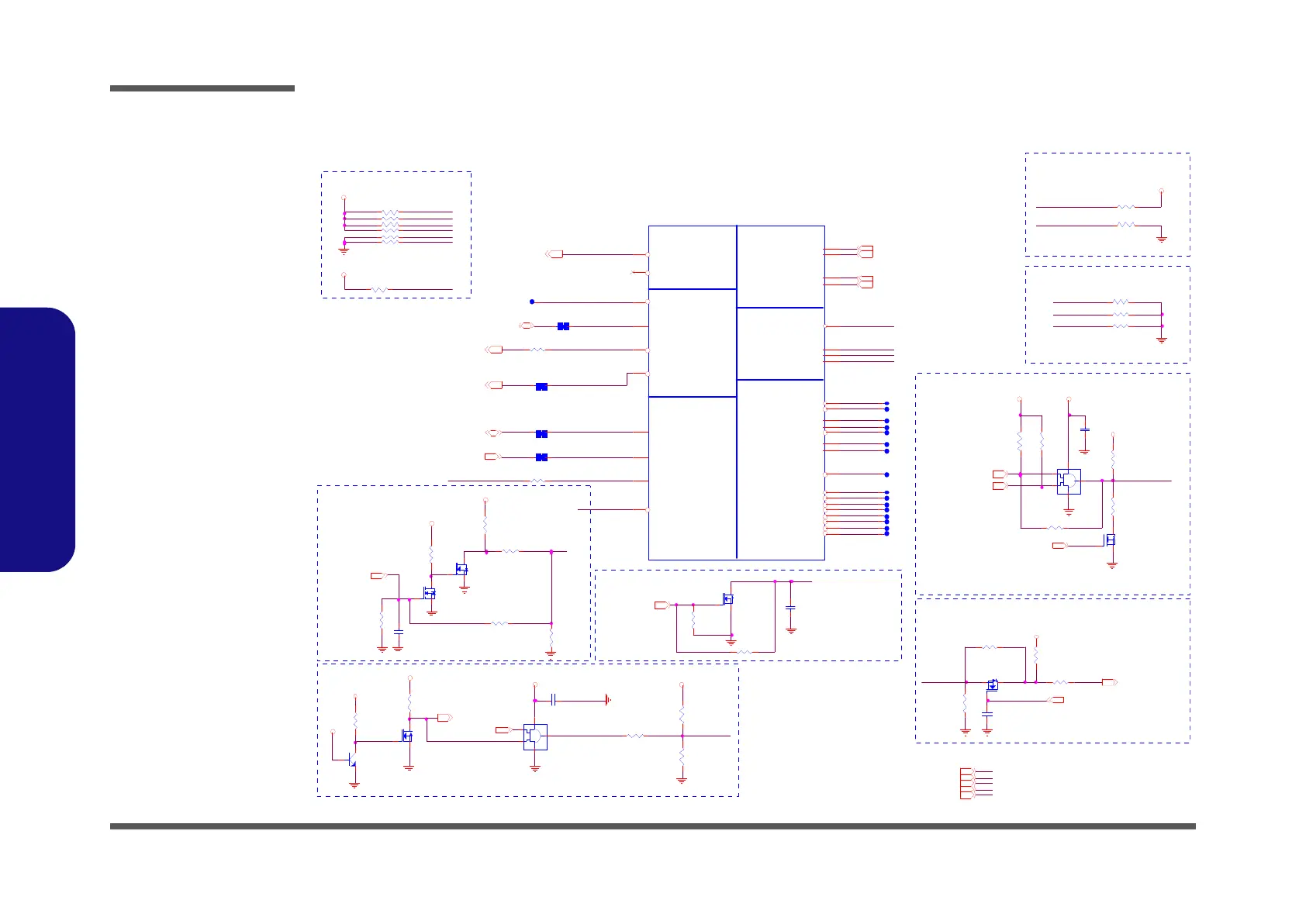

C278

*0.1u_1 6V_Y5V _04

1.05 VS_VTT_ PW R GD37

H_PRO CH OT#

C315

0.047u_10V_X7R _04

R518 *1.5K_1%_04

R517

*750_1%_04

H_ CPU PW R GD _R

S3 ci rcuit:- DRAM PWR GOOD logic

R200 *0_04

R174 130_1%_04

CAD Note: Capacitor need to be placed

close to buffer output pin

U11

*MC 74VH C1G08DF T1G

1

2

5

4

3

R165

*10K _04

3 . 3V _E N _ D

R512

75_04

R152 *1.5K_1%_04

R49 7 *1 0 m il_ s ho rt

R158

*3 K_ 1 % _0 4

R529 200_1%_04

R531 140_1%_04

R528 25.5_1%_04

R166

*10K_04

R496 *10m il_short

R498 *10m il_short

R11 062_04

C 268 *0. 1u_16V_Y 5V _04

Q11

*2N3904

B

E C

R515

43.2_1%_04

R49 910K_04

1.05VS_VTT

R495 *10m il_short

TRACE WIDTH 10MIL, LENGTH <500MILS

H_CPUPWRGD_R

Processor Pullups/Pull downs

H_PROCHOT#

R157

*1.1K_1%_04

R 109 56_1%_04

3.3V

3.3V

3.3V

1.5VS_CP U

1.5VS_CPU

1.05VS _VTT

3.3VS

1.05VS_VTT2,5,23,24,25,35,39

3.3V2,8,11,12,16,18, 19,20,22,23,24,25,27,28,29,30,33,35,37,38,39

CLK_EXP_N 1 9

CLK_EXP_P 19

1.5VS_C PU6,35

CLK_ DP_ P 1 9

CLK_ DP_ N 1 9

H_PROCHOT#39

H_THR MTRIP #23

H_PEC I23,34

H_PM _SY NC20

1.5S _C PU_PWR GD 38

H_C PUPW R GD23

XDP _D BR_R

S

D

G

Q3 7 A

DM N6 0 1D W K-7

2

61

S

D

G

Q37B

D MN 601DW K-7

5

34

H_SNB_IVB#23

SM _RC OMP _2

SM _RC OMP _1

SM _RC OMP _0

XDP _TR ST#

XDP _TC LK

VDD PW RG OO D_R

H_PRO CH OT#_D

XDP _TM S

C PUD RAM RST#

XDP _PR EQ #

XDP _TD I_R

XDP _TD O_R

H_ PM_ SY NC _ R

R52 4

100K _04

Q12

*MTN 7002ZHS3

G

DS

I f PR OCH OT # is n ot u se d, th en i t mu st b e te rmi na te d

w it h a 5 6- O +- 5% p ul l- up re si st or t o 1. 05 VS _VT T .

DDR3 C ompen sation S ignals

BUF_CPU_RST#

SM _R CO MP_1

SM _R CO MP_0

SM _R CO MP_2

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U49B

PZ 98827-364B-01F

SM _ RC OM P[1]

A5

SM _ RC OM P[2]

A4

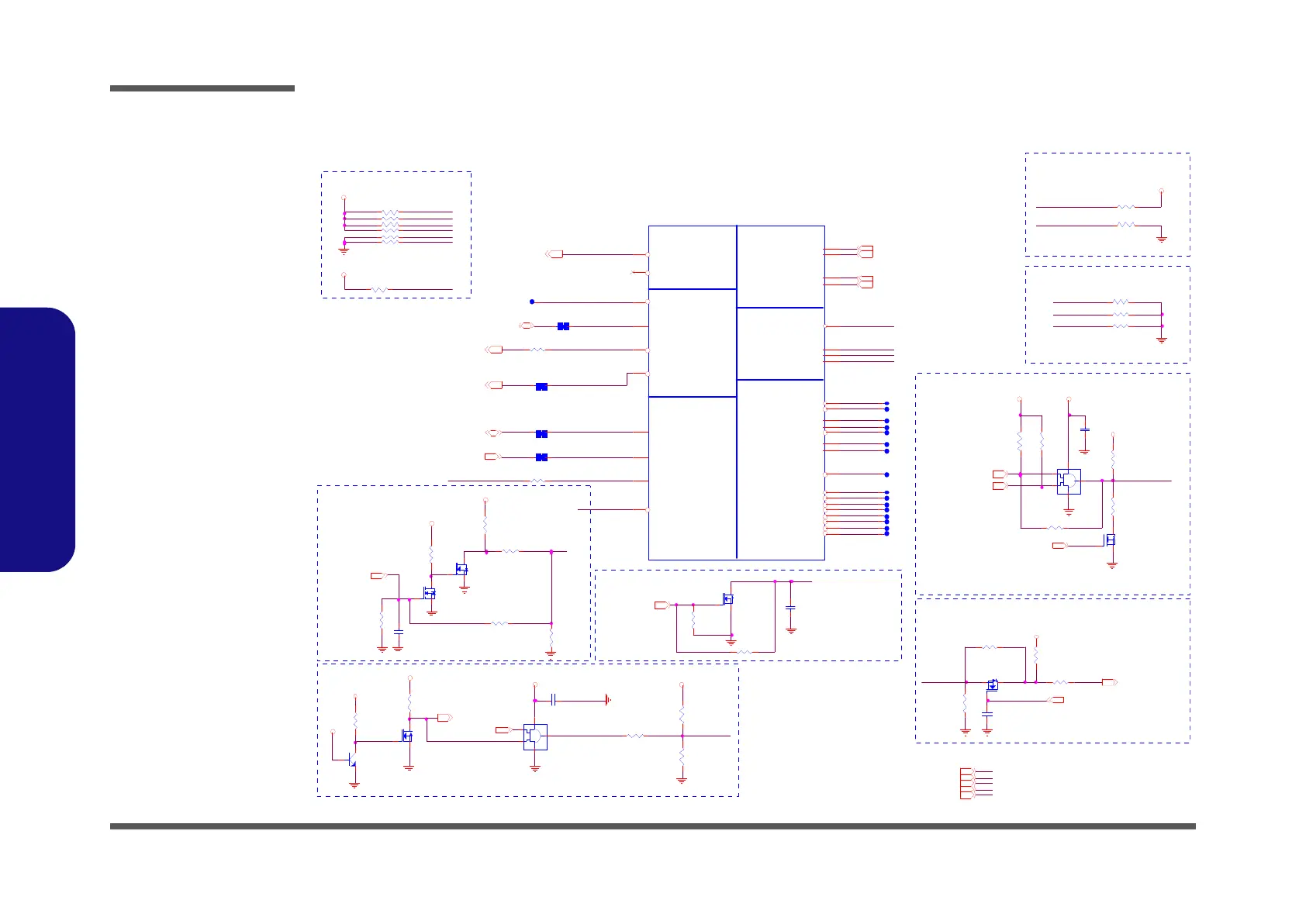

SM_DR AMR ST#

R8

SM _ RC OM P[0]

AK1

BC LK#

A27

BC LK

A28

DPLL_REF_SSC LK#

A15

DPLL_REF_SSC LK

A16

CATERR#

AL33

PEC I

AN33

PR OC HO T#

AL32

THER MTR IP#

AN32

SM _D RA MPW R OK

V8

R ESET#

AR33

PR DY #

AP29

PREQ #

AP27

TCK

AR26

TMS

AR27

TR S T #

AP30

TD I

AR28

TDO

AP26

DBR #

AL35

BPM #[0]

AT2 8

BPM #[1]

AR29

BPM #[2]

AR30

BPM #[3]

AT3 0

BPM #[4]

AP32

BPM #[5]

AR31

BPM #[6]

AT3 1

BPM #[7]

AR32

PM _S YN C

AM34

SKTO CC #

AN34

PR OC _S ELE CT#

C26

UNCOREPWRGOOD

AP33

C621

68p_50V_NPO_04

PLT_RST#12,22,28

VDDPWRGOOD_R

XDP _BP M0 _R

XDP _BP M1 _R

XDP _BP M2 _R

R658

10K _04

1.5V6,8,9,10,25,29,33,35,37,38

XDP _BP M4 _R

XDP _BP M3 _R

XDP _BP M5 _R

XDP _BP M6 _R

XDP _BP M7 _R

XDP _PR DY #

BUF _C PU_R ST#

PM SY S_P W RG D_BUF

C622

47p_50V_N PO_04

R18 6 0 _0 4

H_THR MTRIP #_R

DR AM PW RG D_CP U

H_PR OC HO T# _ EC34

R203

100K _04

Sandy Bridge Processor 2/7 ( CLK,MISC,JTAG )

3.3VS6,9,10,11,12,18,19,20,21,22,23,24,25,27,28, 29,30,31,32,33,34,35,39

Q1 6

MTN 7002ZHS3

G

DS

Buffered reset to CPU

Q1 7

MTN7002ZHS3

G

DS

H_PEC I_ R

R22 5

4.99K_1%_04

CPUDRAMRST#

R231 *0_04

R23 0

1K_04

1.5V

S3 circuit: - DRAM _RST# to memory

should be high during S3

DRAMRST_CNTRL 8,19

R23 5

1K_04

DDR3_DRAMRST# 9,10

R51 351_04

R50 651_04

R51 051_04

R51 151_04

R50 551_04

R50 8*51_04

3.3VS

1.05VS_VTT

R494 1K_04

XD P_TD O_R

XD P _ D B R _ R

H_CATER R#

PU/PD for JTAG signals

XD P_TR ST#

XDP_TMS

H_SNB_IVB#

XD P_PREQ #

XDP_TDI_R

XDP _TC LK

U14

*M C74VHC 1G 08D FT1G

1

2

5

4

3

1. 5S _ C P U _ P W R G D38

PM_D RAM _PW RG D20

3.3V

R187

*200_04

P MSY S_PW RG D_BU F

R188

*1 0 0K _0 4

1.5VS_CP U

R175

200_1%_04

R168

*39_04

Q13

* MTN7002ZH S3

G

DS

SU SB35,37, 38

3.3V

Loading...

Loading...