5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

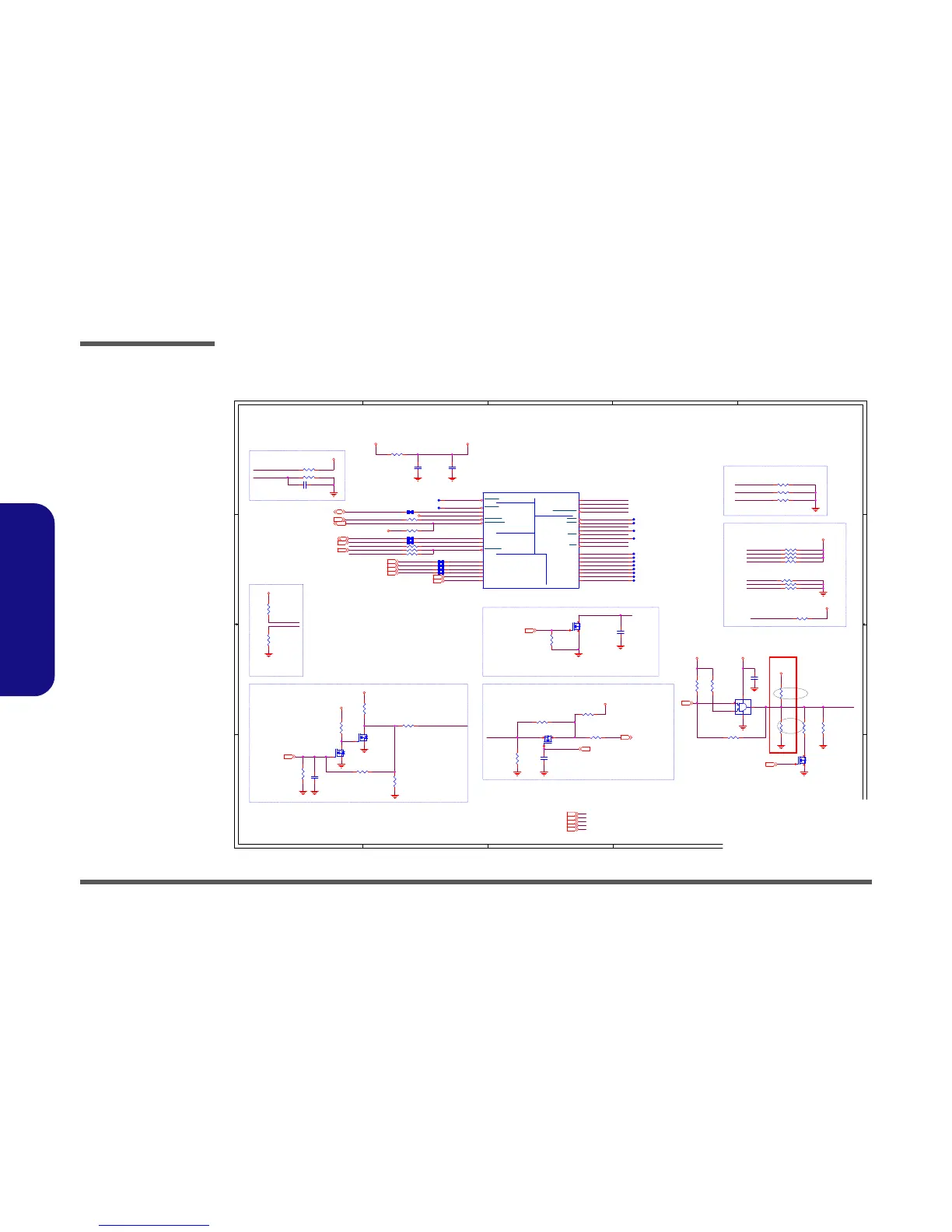

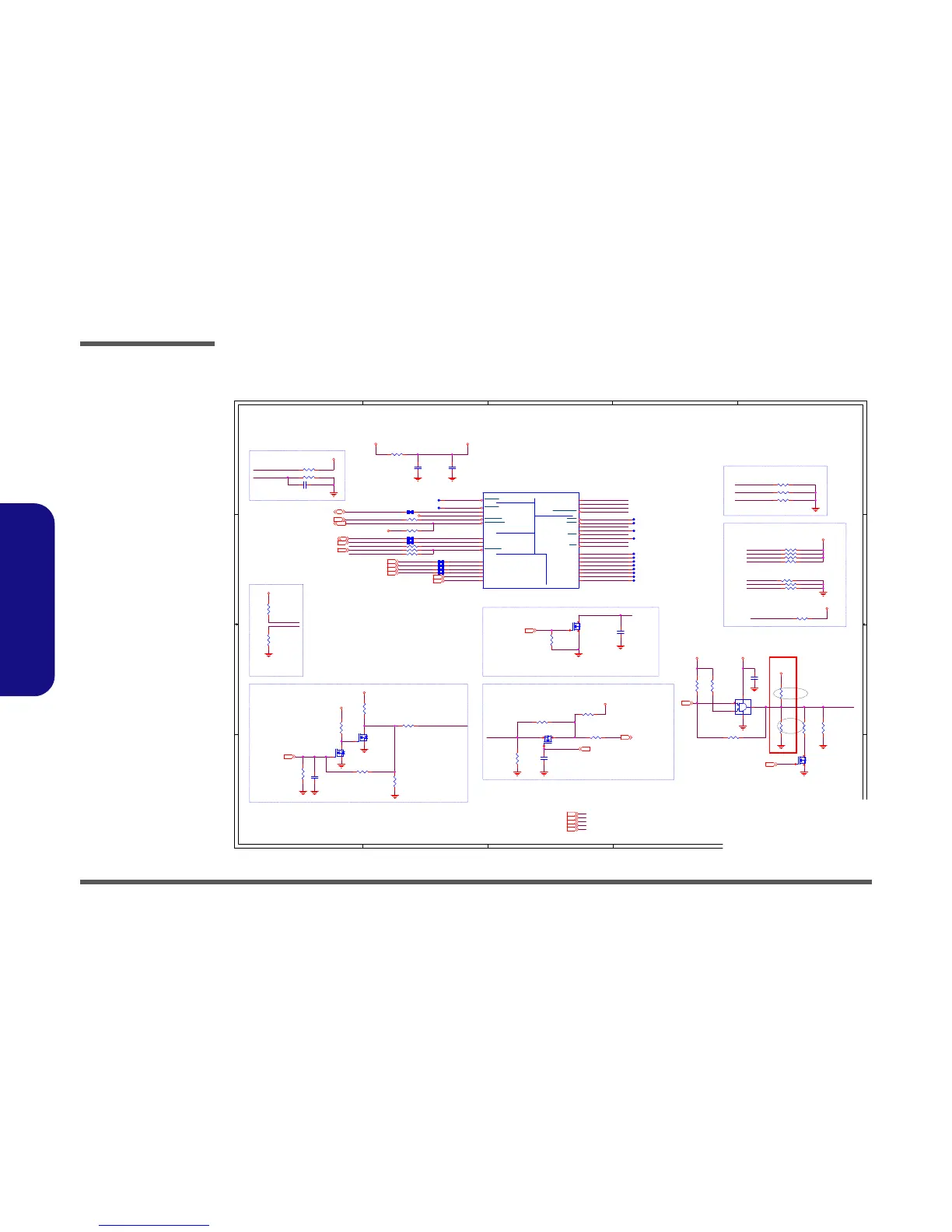

Haswell Processor 2/7 ( CLK,MISC,JTAG )

Buffered reset to CPU

S3 circuit:- DRAM_RST# to memory

should be high during S3

CAD Note: Capacitor need to be placed

close to buffer output pin

TRACE WIDTH 10MIL, LENGTH <500MILS

Processor Pullups/Pull downs

If PROCHOT# is not used,

then it must be terminated

with a 56-ȍ +-5% pull-up

resistor to 1.05VS_VTT .

DDR3 Compensation Signals

S3 circuit:- DRAM PWR GOOD lCIRCUIT

SSC CLOCK TERMINATION

STUFF R4R15 & R4R12

ONLY WHEN SSC CLOCK

NOT USED

PU/PD for JTAG signals

D03

D03

BUF_CPU_RST#

CPUDRAMRST#

SKTOCC#

H_CATERR#

H_P ECI_IS O

H_PROCHOT#_DH_PROCHOT#

H_CPUPWRGD H_CPUPWRGD_R

VDDPWRGOOD_RPMSYS_PWRGD_BUF XDP_DBR_R

XDP_TDO_R

XDP_TDI_R

XDP_TCLK

XDP_TRST#

XDP_TMS

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

CPUDRAMRST#

XDP_PREQ#

XDP_PRDY#

H_PROCHOT#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

PCH_SSC_P

PCH_SSC_N

CPU_RST_N_R

XDP_BPM6

XDP_BPM5

XDP_BPM3

XDP_BPM4

XDP_BPM2

XDP_BPM1

XDP_BPM0

XDP_BPM7

PMSYS_PWRGD_BUF

H_PROCHOT#

H_CPUPWRGD_R

BUF_CPU_RST#

H_THRMTRIP#

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_DBR_R

XDP_TRST#

XDP_TCLK

XDP_TDO_R

XDP_TDO_R

3.3VS

1.05V_LAN_M

3.3V3.3V

+VCCIO_OUT

1.05V_LAN_M +VCCST

+VCCST

+VCCIO_OUT

V_VDDQ_DIMM

V_VDDQ_DIMM

1.05V_LAN_M

1.05V_LAN_M

3.3VS

PLT_RST#25,32

DRAMRST_CNTRL 4,23

DDR3_DRAMRST# 9,10,11

H_PROCHOT#_EC38

H_PECI26,38

H_THRMTRIP#26

H_PM_SYNC24

H_CPUPWRGD26

CLK_EXP_P30

CLK_EXP_N30

PM_DRAM_PWRGD24

SUSB39,41,42

H_PROCHOT#43

PCH_PLTRST_CPU26

PCH_CK_DP_N30

PCH_CK_DP_P30

PCH_SSC_N30

PCH_SSC_P30

1.05V_LAN_M5,28,29,42,44

3.3V2,13,20,22,26,27,28,29,30,31,32,33,37,39,41,44,45

3.3VS6,9,10,11,12,13,22,23,24,25,26,28,29,30,31,32,34,35,36,37,38,39,43,44

+VCCIO_OUT5,6

V_VDDQ_DIMM4,5,9,10,11,41

Title

Size Document Number Rev

Date: Sheet

of

6-71-W35S0-D03

1.0

[03] Haswell 2/7-CLK/MISC

A3

354Tuesday, January 15, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: Sheet

of

6-71-W35S0-D03

1.0

[03] Haswell 2/7-CLK/MISC

A3

354Tuesday, January 15, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: Sheet

of

6-71-W35S0-D03

1.0

[03] Haswell 2/7-CLK/MISC

A3

354Tuesday, January 15, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Haswell rPGA EDS

JTAG

CLOCKTHERMAL

MISC

DDR3

PWR

2 OF 9

U15B

THERMTRIP

AM35

SM_DRAMPWROK

AC10

PLTRSTIN

AT26

SKTOCC

AP32

CATERR

AN32

PECI

AR27

PROCHOT

AM30

DPLL_REF_CLKN

G28

DPLL_REF_CLKP

H28

SSC_DPLL_REF_CLKN

F27

SSC_DPLL_REF_CLKP

E27

BCLKN

D26

BCLKP

E26

SM_RCOMP_0

AP3

SM_RCOMP_1

AR3

SM_RCOMP_2

AP2

SM_DRAMRST

AN3

PRDY

AR29

PREQ

AT29

TCK

AM34

TMS

AN33

TRST

AM33

TDI

AM31

TDO

AL33

DBR

AP33

BPM_N_0

AR30

BPM_N_1

AN31

BPM_N_2

AN29

BPM_N_3

AP31

BPM_N_4

AP30

BPM_N_5

AN28

BPM_N_6

AP29

BPM_N_7

AP28

PWRGOOD

AL34

PM_SYNC

AT28

FC

AK31

Q8

MTN7002ZHS3

G

DS

R12 *10mil_short

R507

*1K_04

R429

*39_04

R36 51_04

R294 *0_04

R346 *10mil_short

C489

*22u_6.3V_X5R_08

R344 *51_04

R458

*200_04

R307 *10mil_short

R34 56_1%_04

R384 *0_04

R433

1K_1%_04

R174 100_1%_04

C558

*0.1u_16V_Y5V_04

R347 *0_04

C539

0.047u_10V_X7R_04

R303

*10K_04

R302 *10mil_short

C40 *0.1u_10V_X5R_04

R527 *1.5K_1%_04

R348 0_04

R437

2K_1%_04

R175 100_1%_04

R312 *100_04

R314 51_04

R13 10K_04

R459

*100K_04

C594

*68p_50V_NPO_04

R33 62_04

R509

*20K_04

Q15

*MTN7002ZHS3

G

DS

R301 *10mil_short

R381 1K_04

R35 *100_04

R25 51_04

R313 51_04

R300

*10K_04

R264

100K_04

R345 *10mil_short

R231K_04

R24 51_04

R526

*100K_04

C491

*22u_6.3V_X5R_08

Q14

MTN7002ZHS3

G

DS

R115 0_04

R508 *43.2_1%_04

R173 75_1%_04

R436 0_04

S

D

G

Q19B

*MTDN7002ZHS6R

5

34

R380 1K_04

U24

*MC74VHC1G08DFT1G

1

2

5

4

3

R511

*10K_04

C398

47p_50V_NPO_04

R306 *10mil_short

R386

4.99K_1%_04

R434

*100K_04

S

D

G

Q19A

*MTDN7002ZHS6R

2

61

Loading...

Loading...