12

12

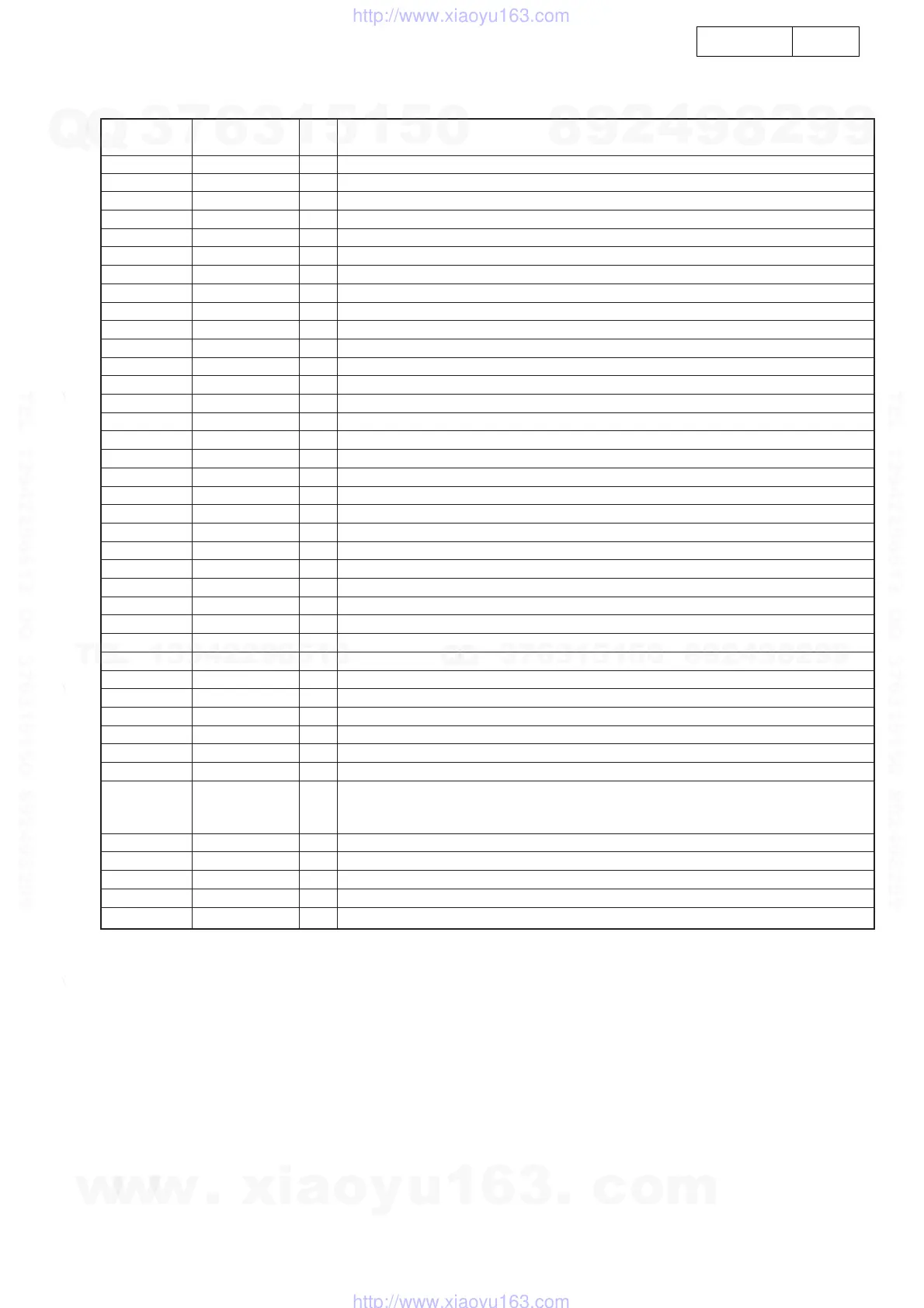

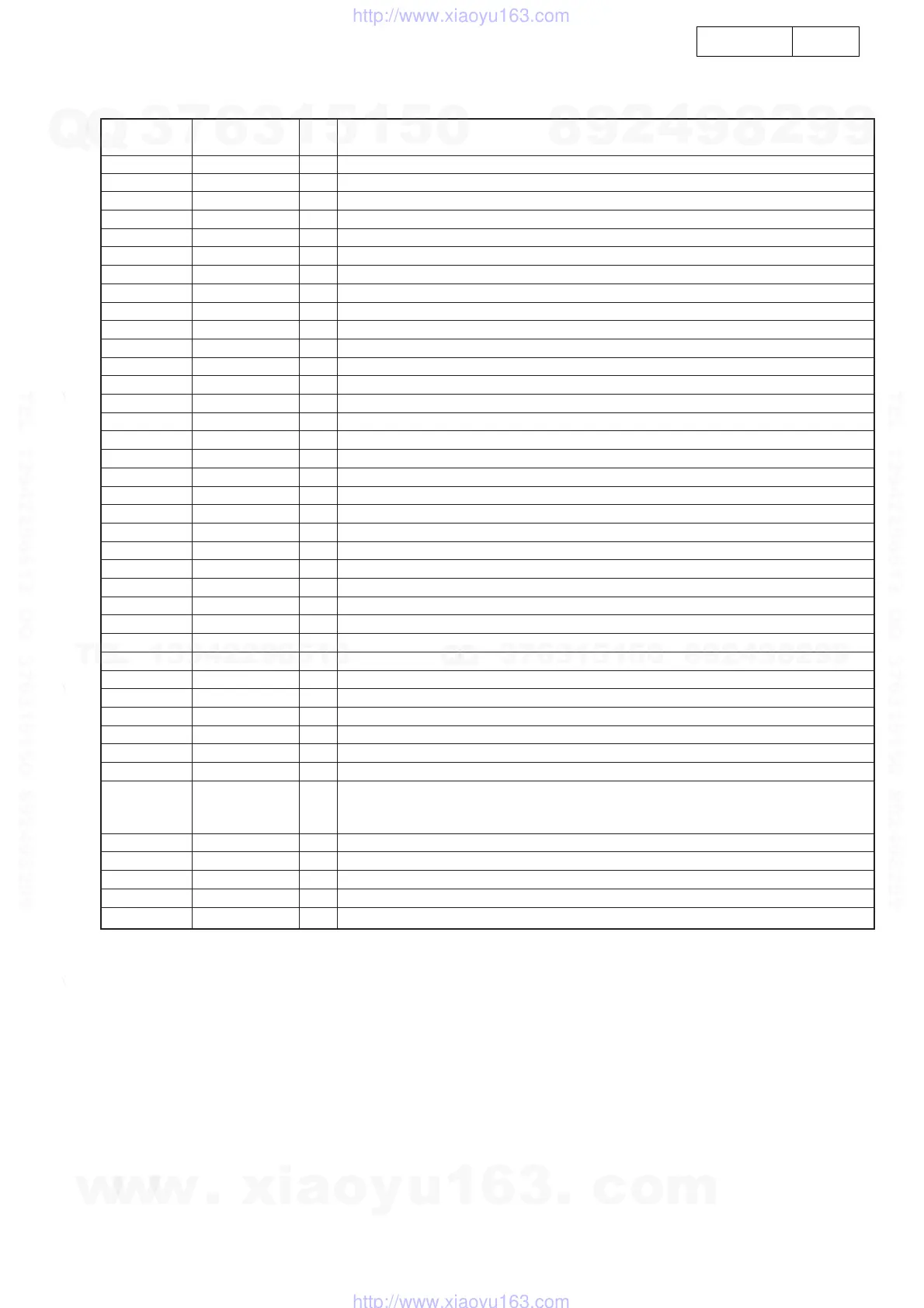

ADV-M71

114 VDAC O Video VDAC output.

115 YUV7 O YUV7 pixel output data.

116 PCLK2XSCN I/O 27 MHz video output pixel clock.

117 PCLKQSCN O 13.5 MHz video output pixel clock.

118 VSYNC# I/O Vertical sync, active low.

119 HSYNC# I/O Horizontal sync, active low.

127:122 HD[5:0] I/O Host data I/O [5:0].

128 HD[6] I/O Host data I/O [6].

131 HD[7] I/O Host data I/O [7].

132 HD[8] I/O Host data bus 8.

133 HD[9] I/O Host data bus line 9.

134 HD[10] I/O Host data bus line 10.

135 HD[11] I/O Host data bus line 11.

136 HD[12] I/O Host data bus line 12.

137 HD[13] I/O Host data bus line 13.

140 HD[14] I/O Host data bus line 14.

141 HD[15] I/O Host data bus line 15.

142 HWRQ# O Host write request.

143 HRRQ# O Host read request.

144 HIRQ I/O Host interrupt.

145 HRST# O Host reset.

146 HIORDY I Host I/O ready.

149 HWR# I/O Host write.

150 HRD# O Host read.

151 HIOCS16# I Device16-bit data transfer.

152 HCS1FX# O Host select 1.

153 HCS3FX# O Host select 3.

158, 155:154 HA[2:0] I/O Host address bus.

160 AUX[0] O I

2

C DATA.

162 AUX[2] I/O Auxiliary ports 2.

165 AUX[3] I/O Auxiliary ports 3.

169:166 AUX[7:3] I/O Auxiliary ports 7:3.

170 LOE# O Device output enable.

176:173 LCS[3:0]# O Chip select [3:0].

197:194,

191:185, LD[15:0] I/O EPROM device data bus.

182:178

198 LWRLL# O Device low-byte write enable.

199 LWRHL# O Device high-byte write enable.

202 CAMIN0 I Camera YUV 0.

203 CAMIN1 I Camera YUV 1.

FunctionI/O

Pin No. Pin Name

161 AUX[1]OI

2

C CLK.

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...