For proper operation of the memory a memory controller and physical layer (PHY) interface needs to be included in the FPGA

design. The Xilinx 7-series memory interface solutions core generated by the MIG (Memory Interface Generator) Wizard hides

away the complexities of a DDR3 interface. Depending on the tool used (ISE, EDK or Vivado) the MIG Wizard can generate

a native FIFO-style or an AXI4 interface to connect to user logic. This workflow allows the customization of several DDR3

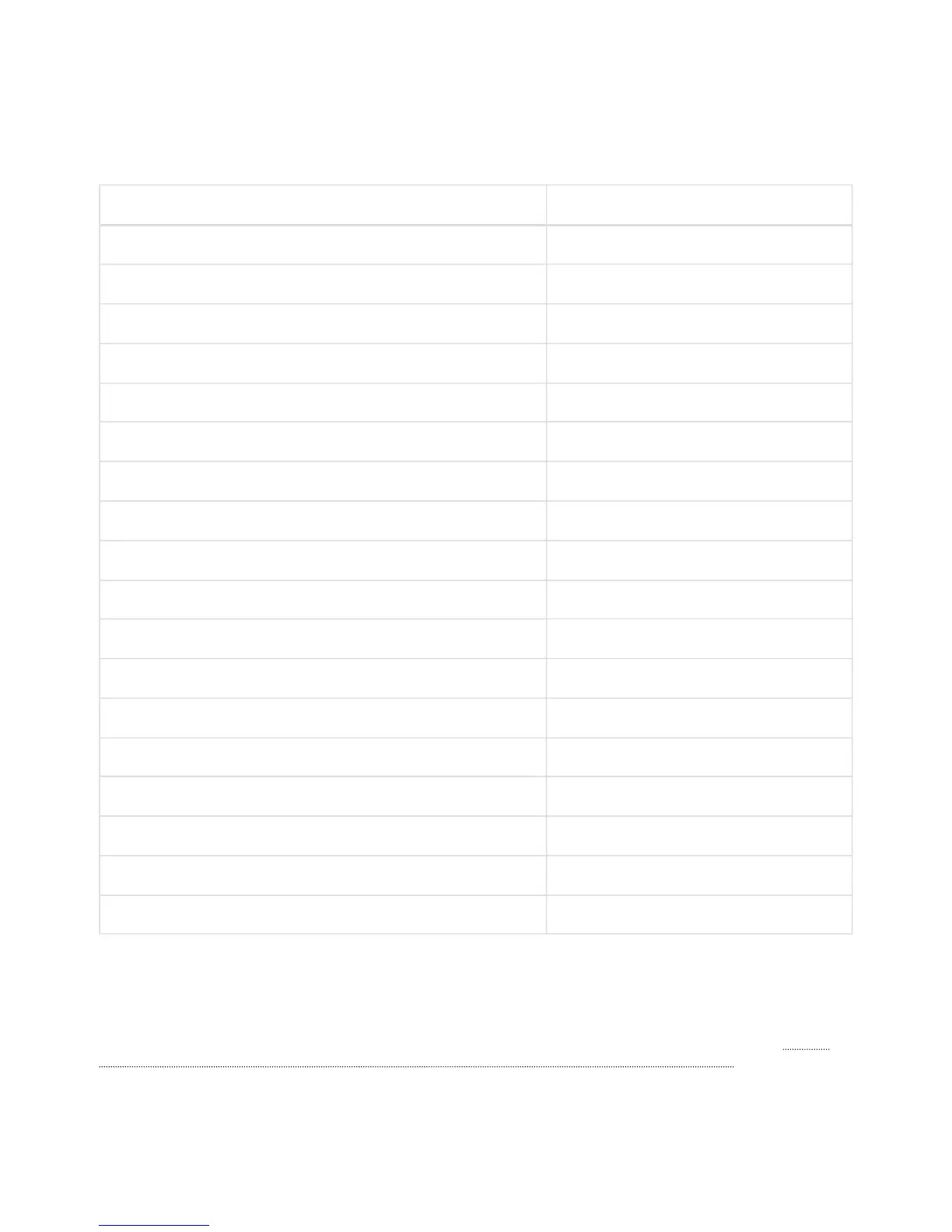

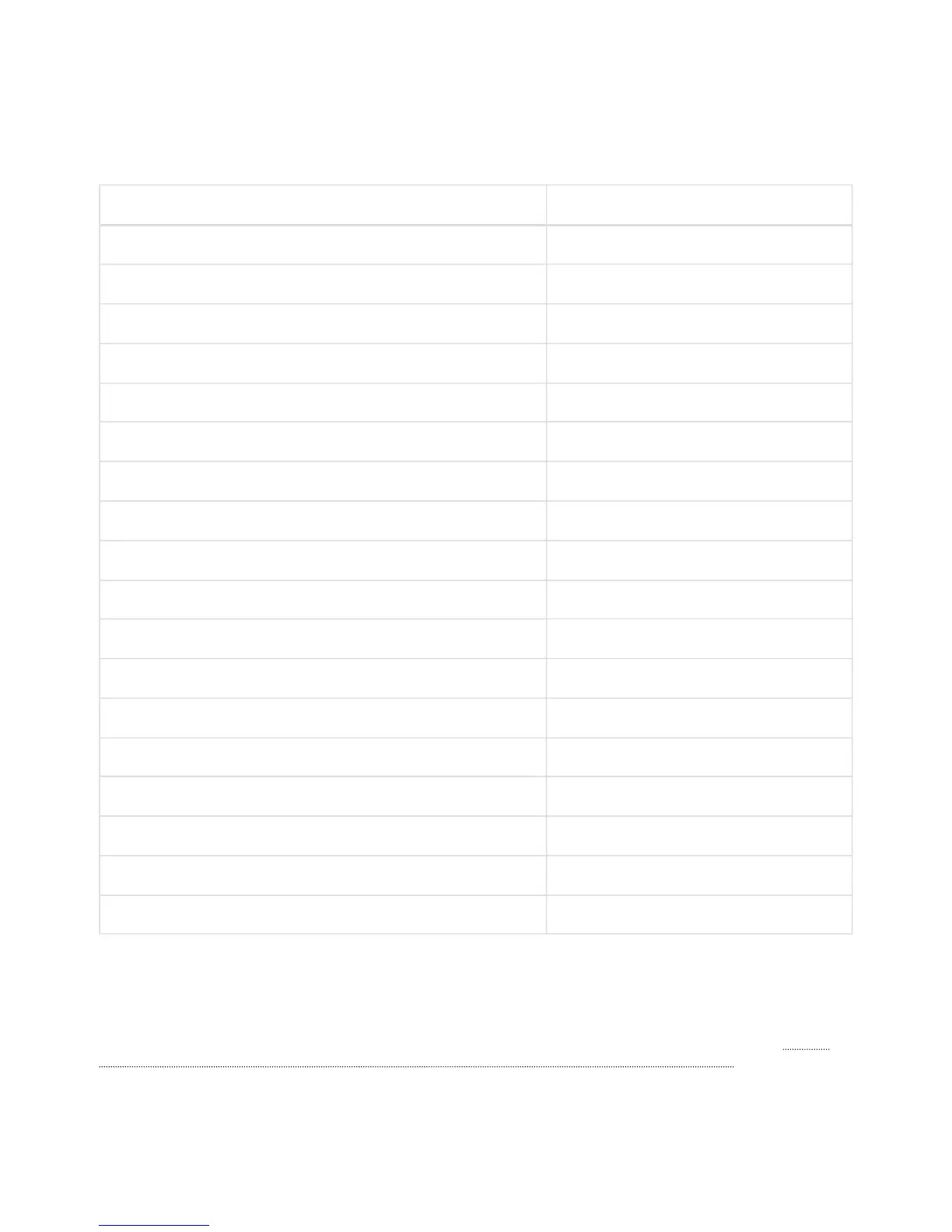

parameters optimized for the particular application. Table 4 below lists the MIG Wizard settings optimized for the Genesys 2.

Setting Value

Memory type DDR3 SDRAM

Max. clock period 1112ps (~900MHz)

Max. data rate ~1800Mbps

Clock ratio 4:1

VCCAUX_IO 2.0V

Memory type Components

Memory part MT41J256M16XX-107

Memory voltage 1.5V

Data width 32

Data mask Enabled

Input clock period 5004ps (~200MHz)

Output driver impedance RZQ/7

Chip Select pin Enabled

Rtt (nominal) – On-die termination RZQ/6

Internal Vref Disabled

Reference clock Use system clock

Internal termination impedance N/A

DCI cascade Disabled

Table 4. DDR3 settings for the Genesys 2.

The MIG Wizard will require the fixed pin-out of the memory signals to be entered and validated before generating the IP

core. For your convenience an importable UCF/XDC file is provided on the Digilent website to speed up the process.

For more details on the Xilinx memory interface solutions refer to the 7 Series FPGAs Memory Interface Solutions

User

Guide (ug586) (http://www.xilinx.com/support/documentation/ip_documentation/mig_7series/v2_1/ug586_7Series_MIS.pdf).

6.2. Quad-SPI Flash

Page 1

of 3

Loading...

Loading...