Chapter 3

H61H2-M4 USER MANUAL

50

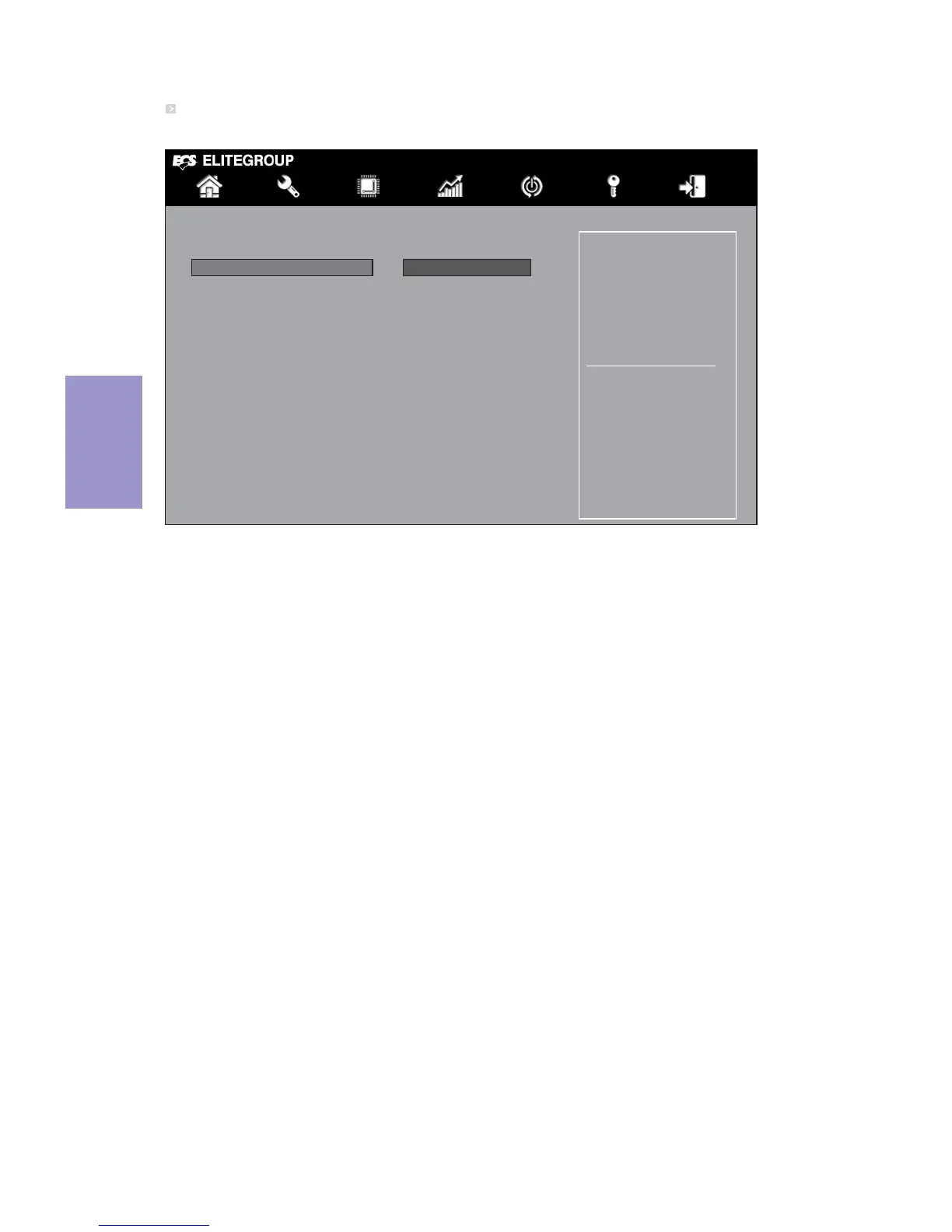

Chipset OverClocking Configuration

Scroll to this item to view the following screen:

Main Advanced Chipset M.I.B III Boot Security Exit

The selection of

Performance Memory

Profiles which impacts

memory sizing behavior.

Memory Multiplier Configuration

Performance Memory Profiles Automatic

XMP Profile1 Supported

XMP Profile2 Not Supported

Memory Timing Configuration

CAS# Latency (tCL) 9

RAS# to CAS# Delay (tRCD) 9

Row Precharge Time (tRP) 9

RAS# Active Time (tRAS) 24

Write Recovery Time (tWR) 10

Row Refresh Cycle Time (tRFC) 74

Active to Active Delay (tRRD) 4

Write to Read Delay (tWTR) 5

Read CAS# Precharge (tRTP) 5

Four Active Window Delay (tFAW) 20

+/- : Change Opt.

Enter/Dbl Click : Select

: Select Screen

/Click: Select Item

F1: General Help

F2: Previous Values

F3: Optimized Defaults

F4: Save & Exit

ESC/Right Click: Exit

Row Precharge Time (tRP) (9)

This item specifies Row precharge to Active or Auto-Refresh of the same bank.

CAS Latency (tCL) (9)

This item determines the operation of DDR SDRAM memory CAS (colulmn address

strobe). It is recommended that you leave this item at the default value. The 2T

setting requires faster memory that specifically supports this mode.

Performance Memory Profiles (Automatic)

This item allows you to select the memory mode: Automatic, Manual, XMP Profile 1

or 2.

RAS# to CAS# Delay (tRCD) (9)

This item specifies the RAS# to CAS# delay to Rd/Wr command to the same bank.

Row Refresh Cycle Time (tRFC) (74)

This item specifies the row refresh cycle time.

RAS# Active Time (tRAS) (24)

This item specifies the RAS# active time.

Write Recovery Time (tWR) (10)

This item specifies the write recovery time.

Write to Read Delay (twTR) (5)

This item specifies the write to read delay time.

XMP Profile 1/2 (Supported/Not Supported)

These items show the information of Performance Memory Profiles.

Active to Active Delay (tRRDmin) (4)

This item controls the ACTIVE bank x to ACTIVE bank y in memory clock cycles.

Loading...

Loading...