Revision B 120 Series Maternal/Fetal Monitor 4-21

2015590-001

Theory of Operation: Main Motherboard

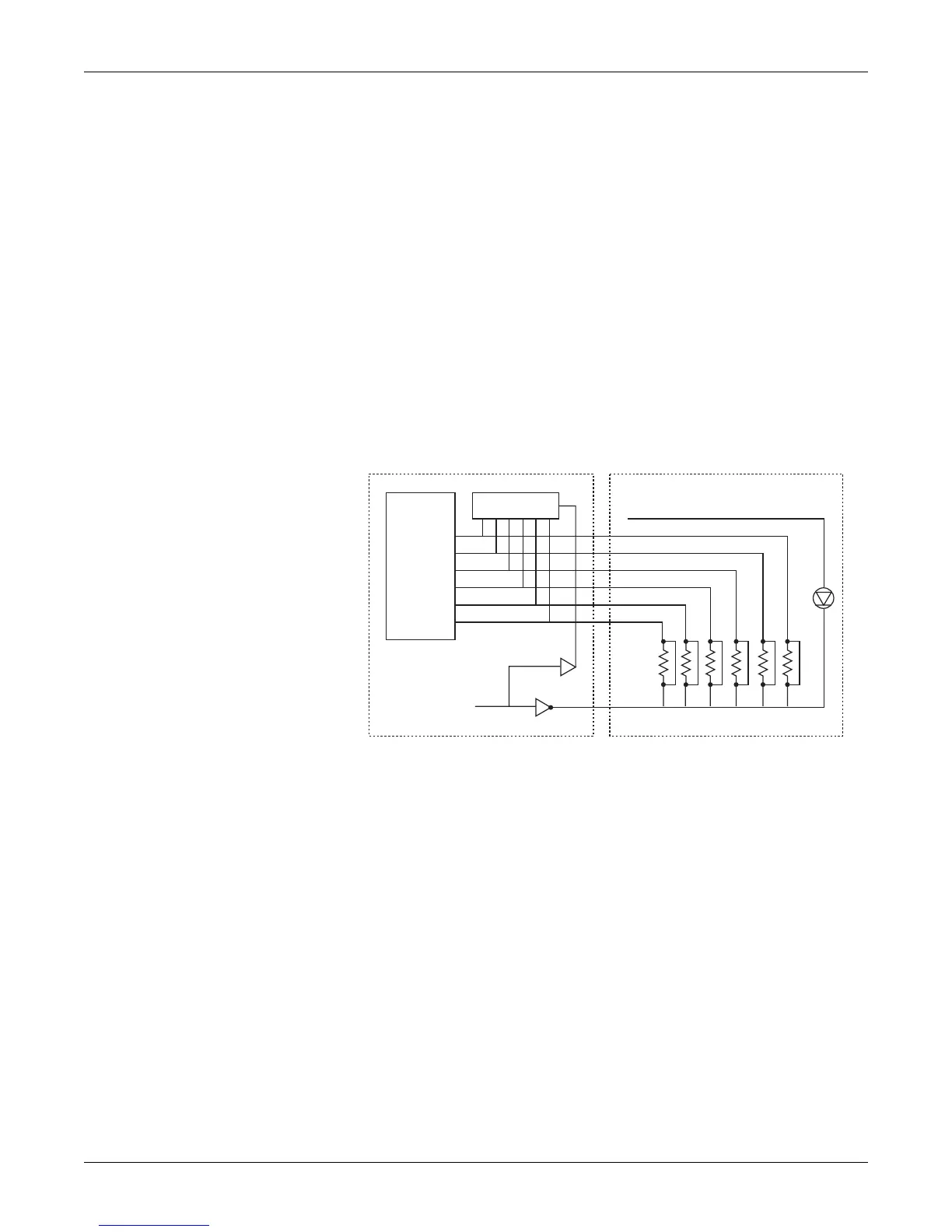

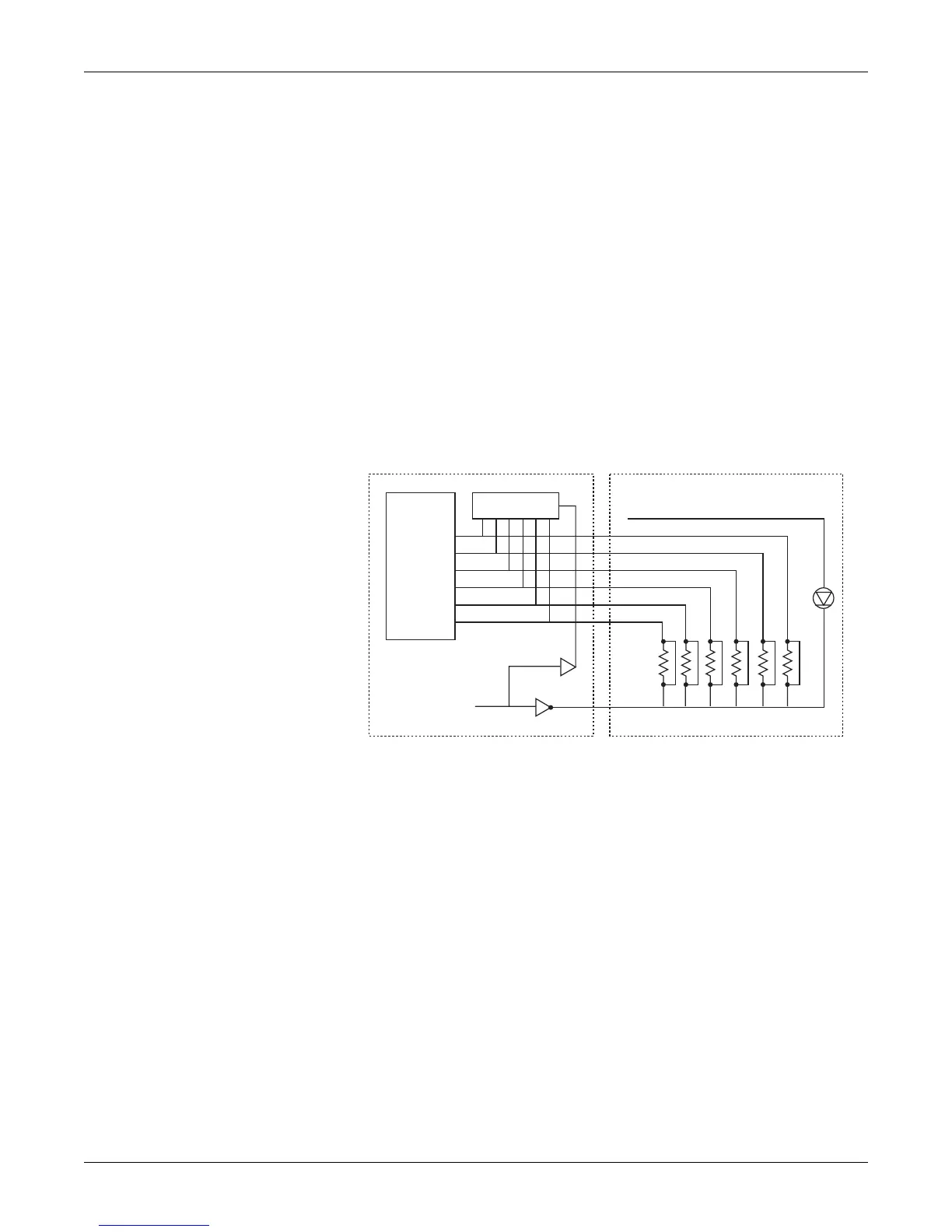

The 7960 encoder/decoder operates in mode 0, thus inserting its own preamble and

removing it at the receiver end. On the receiving end, the CS/ line becomes active

along with the receive clock after the preamble is stripped off, thus enabling the

USART. For transmission, a carrier avoidance scheme is accomplished through

16V8 PAL (U34) and 7960 ACD/ and RTS/ lines. The 7960 will transmit whenever

the RTS/ line is pulled low. The advanced carrier detect line (ACD/), is gated along

with an RTS enable from control latch U22 and processor USART RTS/ line to only

turn on the 7960 RTS/ line when ACD/ is inactive (QUIET LINE). Both the transmit

and the receive clocks are provided by the 7960. The address detection circuitry

consists of a buffer (U17), series resistors (R30–R35) and capacitors (C120–C125)

for static protection, and address checking logic in U29. The address checking is

done by reversing the GND and pull-up voltages (through the TEST line), and

reading back all 1s if lines are not broken. If any line is broken (pull-up single in-line

package, RN1, pulled low for TEST and GND line pulled high), then a 0 will be

detected. Normal reading of the address selects the pull-up single in-line package

high and GND line low. Refer to Figure 4-5.

Figure 4-5. Corolan Address Checking

Receive

Buffer

4.7 kW Single In-

Line Package

TEST*

GND

4.7 k

W Resistors and Shorting Jumpers

LED

ADR0

LED

ADR5

ADR4

ADR3

ADR2

ADR1

2120is Series Monitor

Bedside Wallplate

Loading...

Loading...