Interrupts

The device provides both external interrupt and internal Timer/Event Counter interrupt functions.

The Interrupt Control Register (INTC;0BH) contains the interrupt control bits to set the enable/dis

-

able and the interrupt request flags.

Interrupt Register

Once an interrupt subroutine is serviced, all the other interrupts will be blocked (by clearing the

EMI bit). This scheme may prevent any further interrupt nesting. Other interrupt requests may oc

-

cur during this interval but only the interrupt request flag is recorded. If a certain interrupt requires

servicing within the service routine, the EMI bit and the corresponding bit of the INTC may be set to

allow interrupt nesting. If the stack is full, the interrupt request will not be acknowledged, even if the

related interrupt is enabled, until the Stack Pointer is decremented. If immediate service is desired,

the stack must be prevented from becoming full.

All of these interrupts have the capability of waking up the processor when in the Power Down

Mode. As an interrupt is serviced, a control transfer occurs by pushing the Program Counter onto

the stack, followed by a branch to a subroutine at a specified location in the Program Memory.

Only the Program Counter is pushed onto the stack. If the contents of the register or status register

are altered by the interrupt service program, which may corrupt the desired control sequence, then

the contents should be saved in advance.

32

Cost-Effective I/O Type MCU

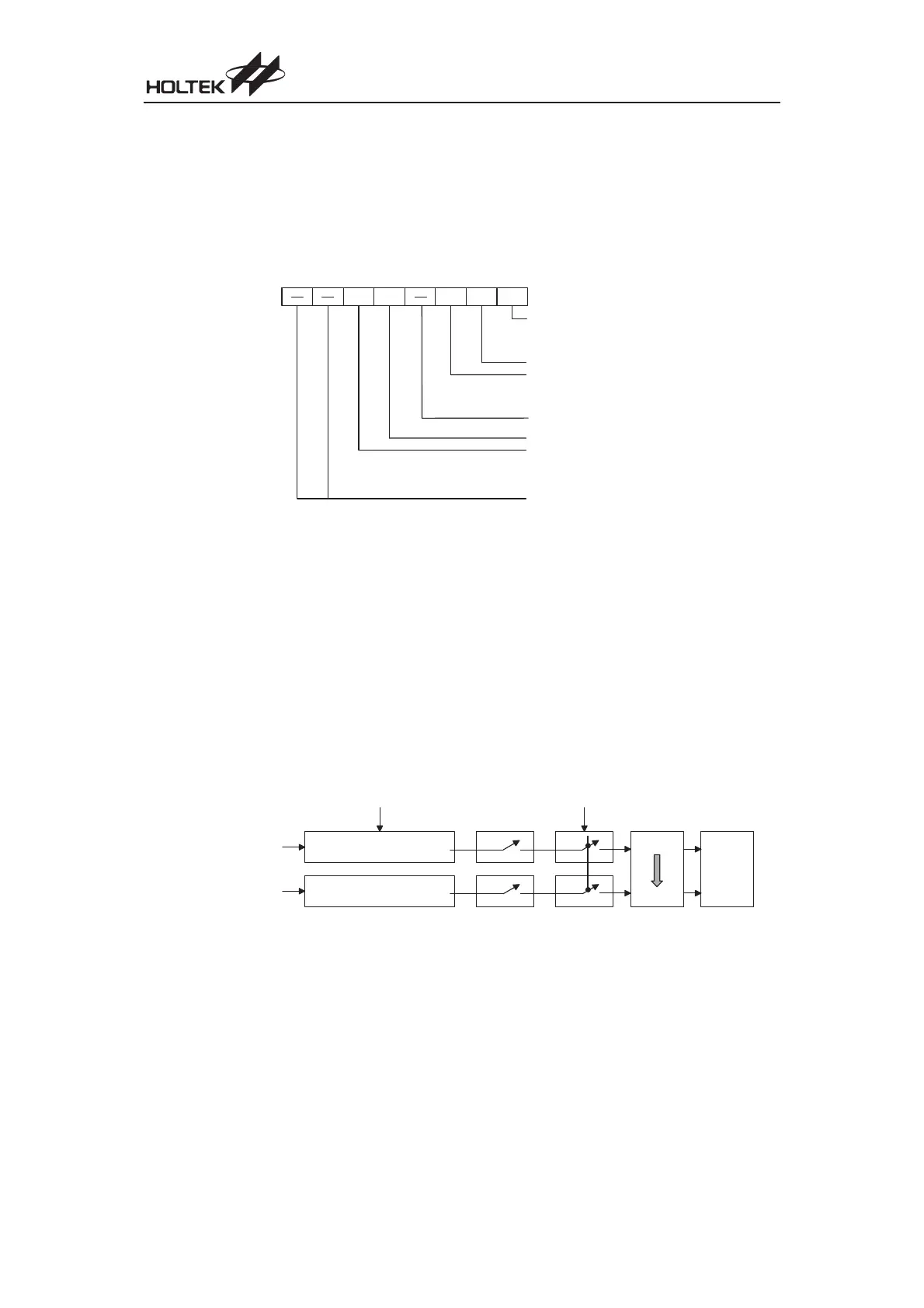

A u t o m a t i c a l l y C l e a r e d b y I S R

M a n u a l l y S e t o r C l e a r e d b y S o f t w a r e

E x t e r n a l I n t e r r u p t

R e q u e s t F l a g E I F

T i m e r / E v e n t C o u n t e r

I n t e r r u p t R e q u e s t F l a g T F

E E I

E T I

E M I

P r i o r i t y

I n t e r r u p t

P o l l i n g

H i g h

L o w

A u t o m a t i c a l l y D i s a b l e d b y I S R

C a n b e E n a b l e d M a n u a l l y

Interrupt Scheme

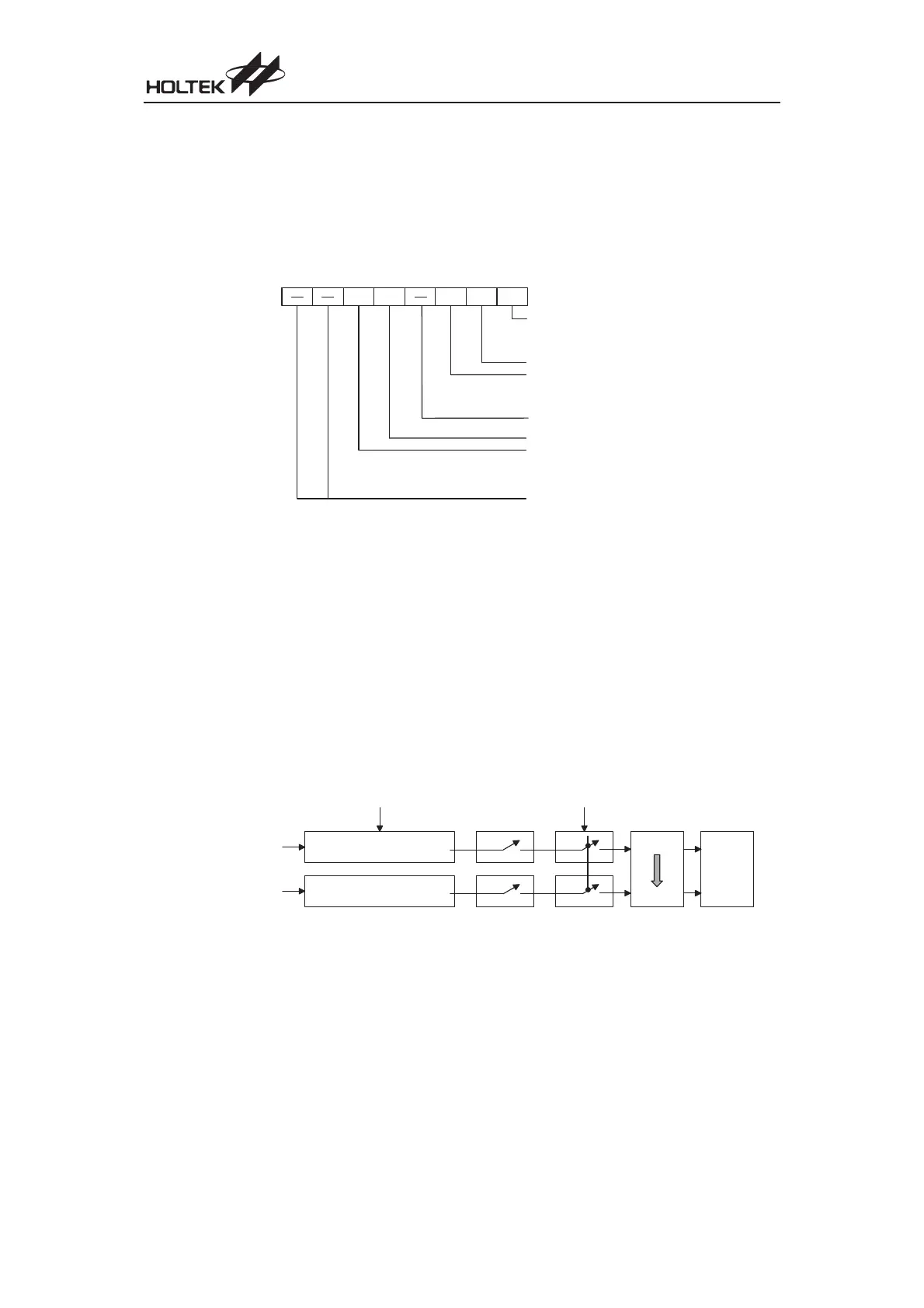

I N T C R e g i s t e r

M a s t e r I n t e r r u p t G l o b a l E n a b l e

1 : g l o b a l e n a b l e

0 : g l o b a l d i s a b l e

N o t i m p l e m e n t e d , r e a d a s " 0 "

b 7 b 0

E T I E E I E M I

E x t e r n a l I n t e r r u p t E n a b l e

T i m e r / E v e n t C o u n t e r I n t e r r u p t E n a b l e

1 : e n a b l e

0 : d i s a b l e

E x t e r n a l I n t e r r u p t R e q u e s t F l a g

T i m e r / E v e n t C o u n t e r I n t e r r u p t R e q u e s t F l a g

1 : r e q u e s t i s s u e d

0 : r e q u e s t n o t i s s u e d

E I F T F

N o t i m p l e m e n t e d , r e a d a s " 0 "

Loading...

Loading...