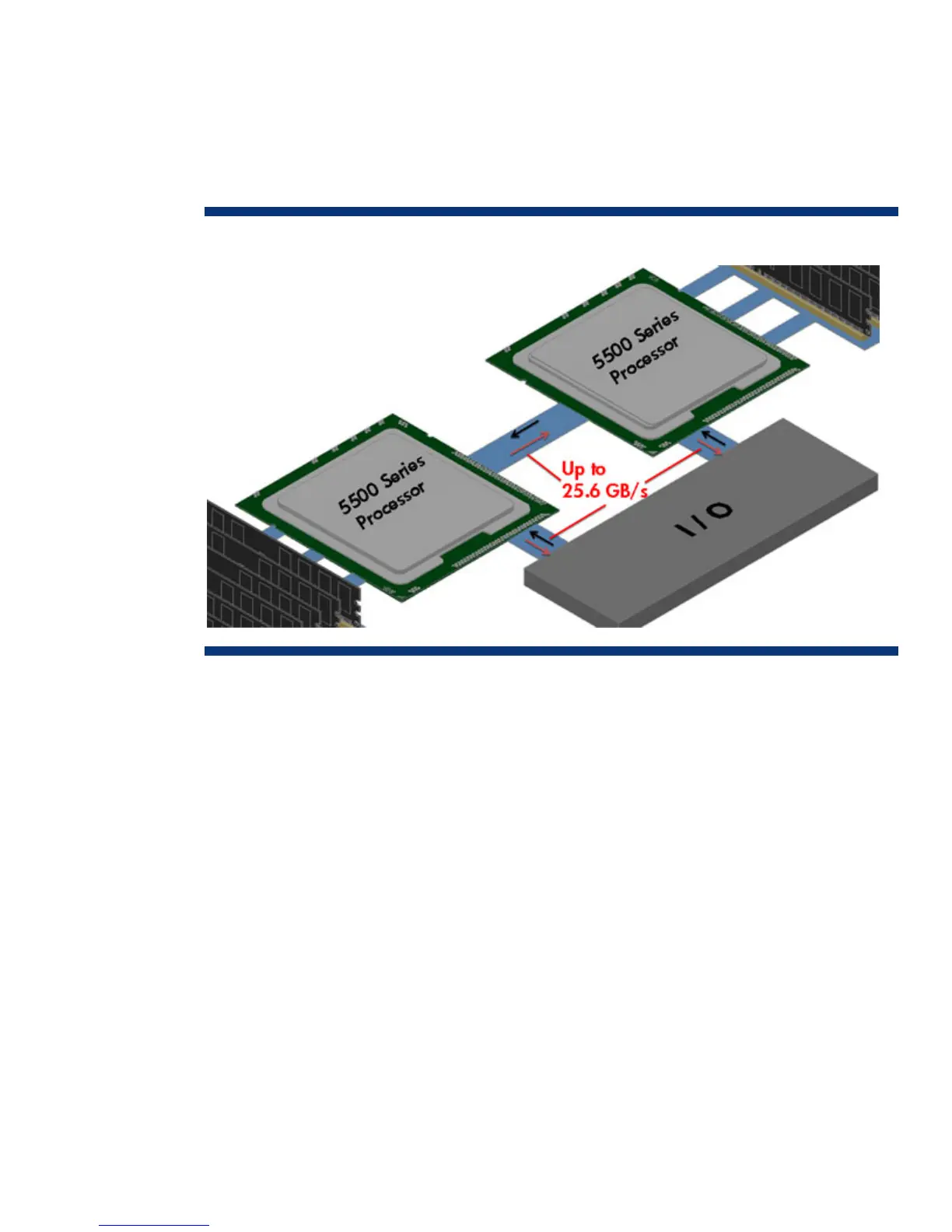

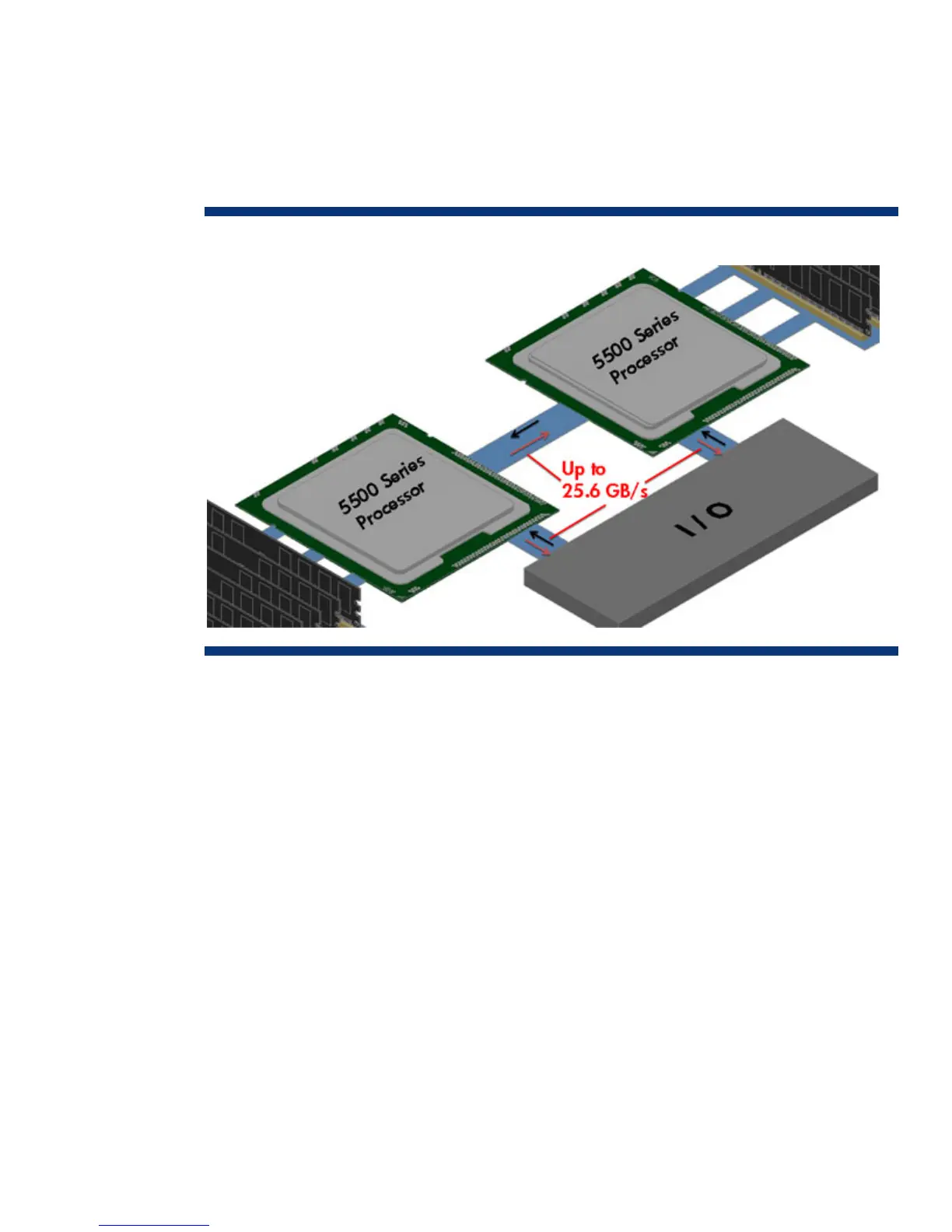

Each link is comprised of twenty 1-bit lanes. A maximum of 16 bits are used to transfer data; the

remaining 4 bits are used for the protocol and error correction. The interconnect performs a maximum

of 6.4 gigatransfers per second and has a bandwidth of 12.8-gigabytes per second in each

direction, for a total bandwidth of 25.6 gigabytes per second.

If an application requests data from the memory of another processor, the QuickPath interconnect

uses high-bandwidth inter-processor communication to retrieve the data.

Figure 2. Block diagram of QuickPath architecture

Hyper Threading

Simultaneous Multi-threading Technology, or SMT, is an enhanced version of Intel’s Hyper-Threading

Technology. SMT lets each core execute two computational threads at the same time. A single

processor can execute up to eight threads simultaneously (Figure 3). Compared to the previous Intel

core architecture, the high-bandwidth memory subsystem supplies data faster to the two computational

processes, and the low-latency cache hierarchy allows more instructions to be processed

simultaneously.

5

Loading...

Loading...