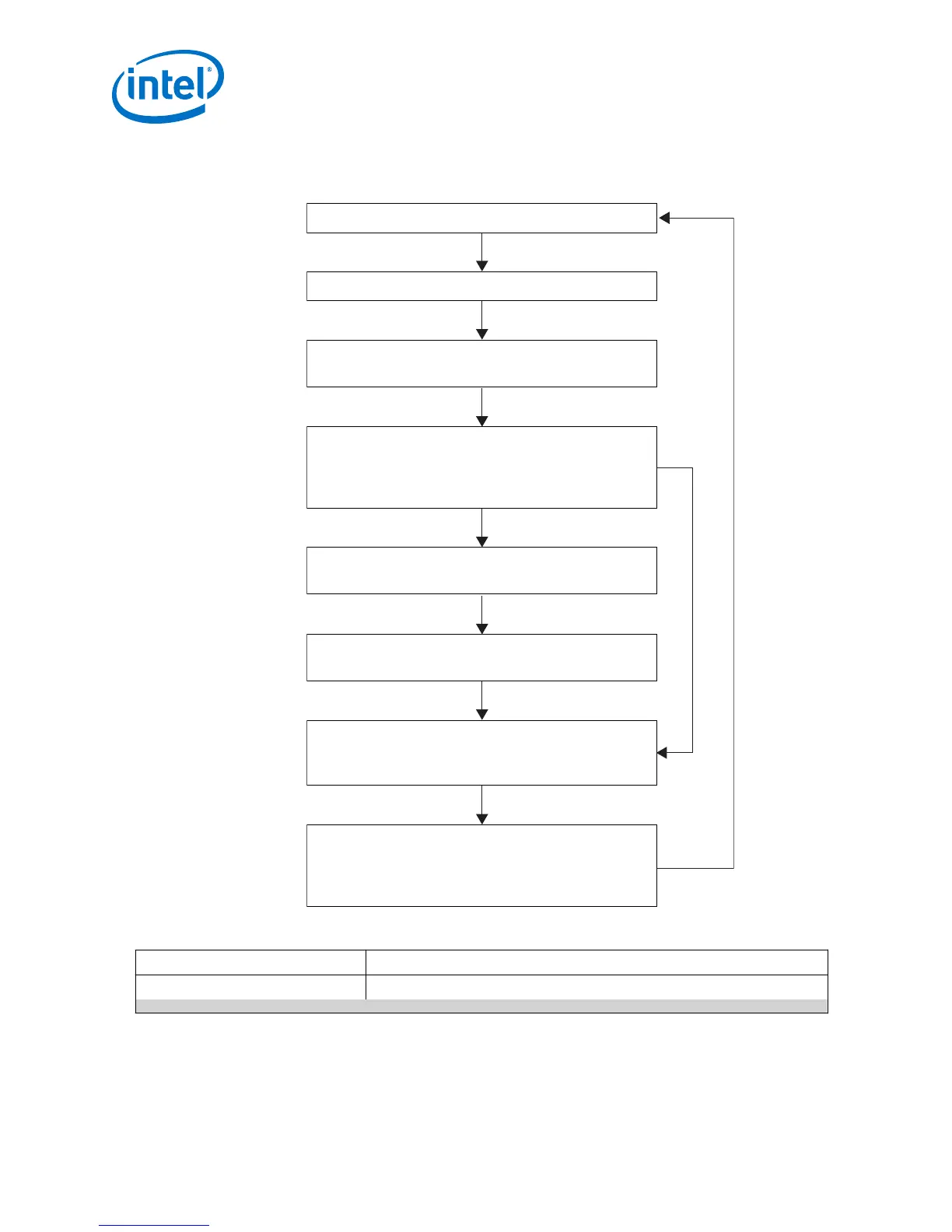

Figure 7. Multi-Rate Reconfiguration Sequence Flow

Reset the RX HDMI PLL and RX transceiver.

Enable the rate detection circuit to measure incoming TMDS clock.

Accept acknowledgement with clock frequency band and desired

RX HDMI PLL and RX transceiver settings.

Determine if RX HDMI PLL and/or RX transceiver reconfiguration

is required based on the previous and current detected clock

frequency band and color depth. Different color depths may fall

within the same clock frequency band.

Request RX HDMI PLL and/or RX transceiver reconfiguration if the

previous and current clock frequency band or color depth differs.

The controller reconfigures the RX HDMI PLL and/or RX transceiver

(followed by recalibration on Intel Arria 10 device).

Reconfiguration Required

Reconfiguration

Not Required

When all reconfiguration processes complete or the previous and

current clock frequency band and color depth do not differ, reset

the RX HDMI PLL and RX transceiver.

Enable rate the detection circuit periodically to monitor the

reference clock frequency. If the clock frequency band changes or

the RX HDMI PLL or RX transceiver or HDMI core lose lock, repeat

the process.

Table 8. HDMI TX Top Components

continued...

Loading...

Loading...