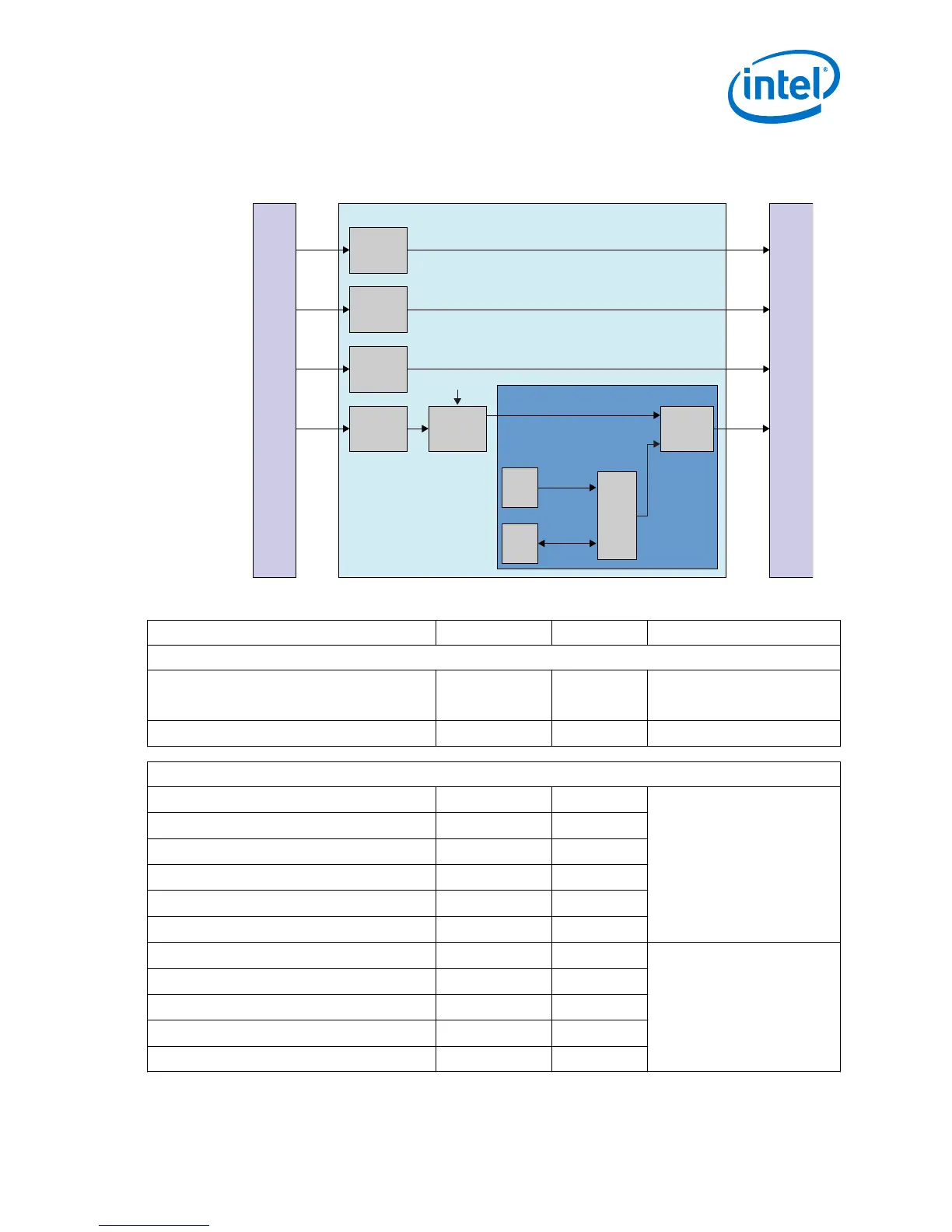

Figure 9. RX-TX Link with Dynamic Range and Mastering InfoFrame Insertion

The figure shows the block diagram of RX-TX link including Dynamic Range and Mastering InfoFrame insertion

into the HDMI TX core auxiliary stream.

HDMI RX

Top

HDMI TX

Top

Auxiliary

Packet Filter

Video

Bypass FIFO

Audio

Bypass FIFO

Sideband

Bypass FIFO

Auxiliary

Bypass FIFO

Auxiliary

Packet

Generator

Multiplexer

In1

In0

HDR

Data

AUX

Insertion

Control

Auxiliary Data Insertion Block

Auxiliary Data Interface

Auxiliary InfoFrame

Content Interface

Auxiliary Insertion

Control Interface

block_ext_hdr_infoframe

RX Video

TX Video

RX Audio

TX Audio

RX Sideband

TX Sideband

RX Auxiliary

TX Auxiliary

RX-TX Link

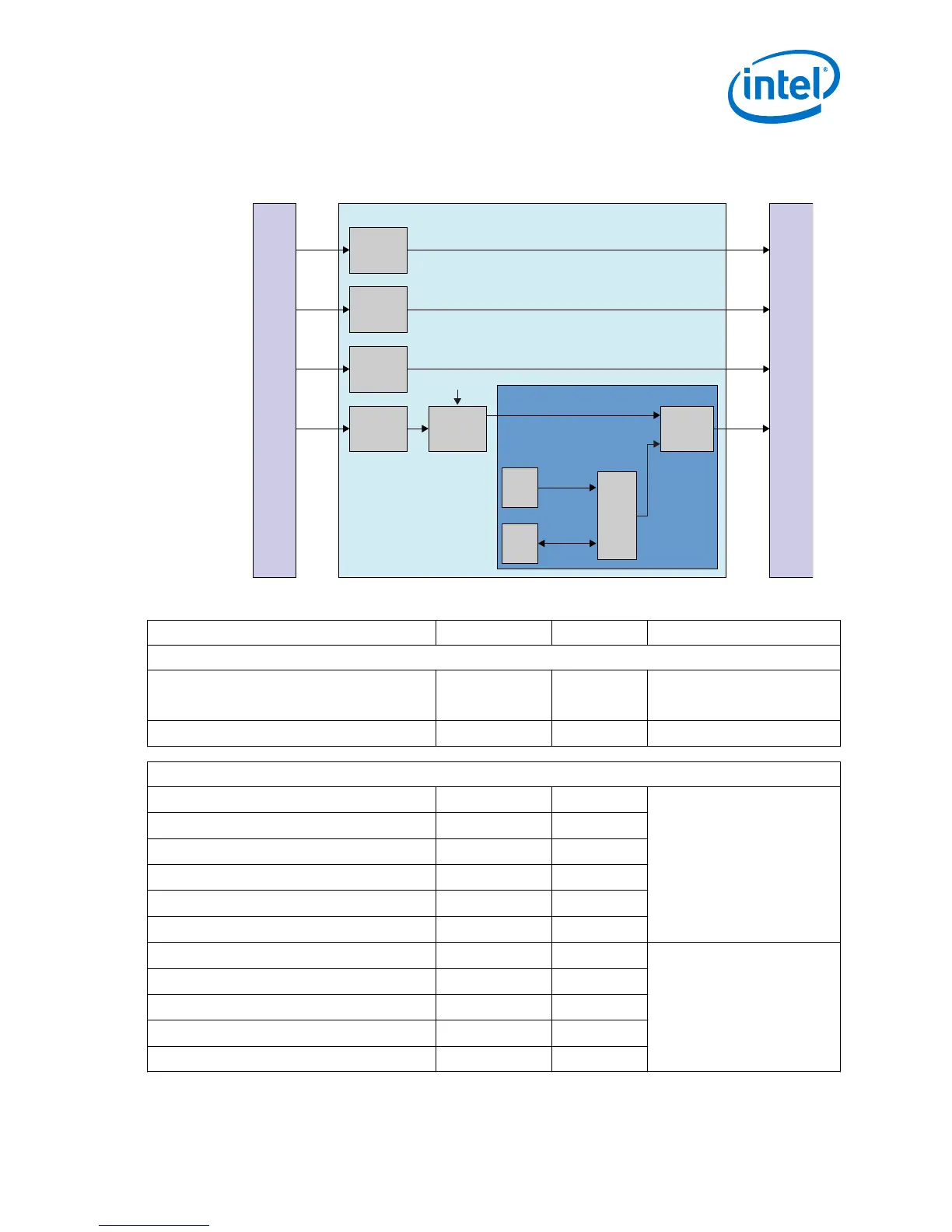

Table 11. Auxiliary Data Insertion Block (altera_hdmi_aux_hdr) Signals

Signal Direction Width Description

Clock and Reset

clk_clk

Input 1 Clock input. This clock should be

connected to the link speed

clock.

reset_reset_n

Input 1 Reset input.

Auxiliary Packet Generator and Multiplexer Signals

multiplexer_out_data

Output 72 Avalon streaming output from

the multiplexer.

multiplexer_out_valid

Output 1

multiplexer_out_ready

Output 1

multiplexer_out_startofpacket

Output 1

multiplexer_out_endofpacket

Output 1

multiplexer_out_channel

Output 11

multiplexer_in_data

Input 72 Avalon streaming input to the

In1 port of the multiplexer.

multiplexer_in_valid

Input 1

multiplexer_in_ready

Input 1

multiplexer_in_startofpacket

Input 1

multiplexer_in_endofpacket

Input 1

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

21

Loading...

Loading...