Language Dictionary - 4

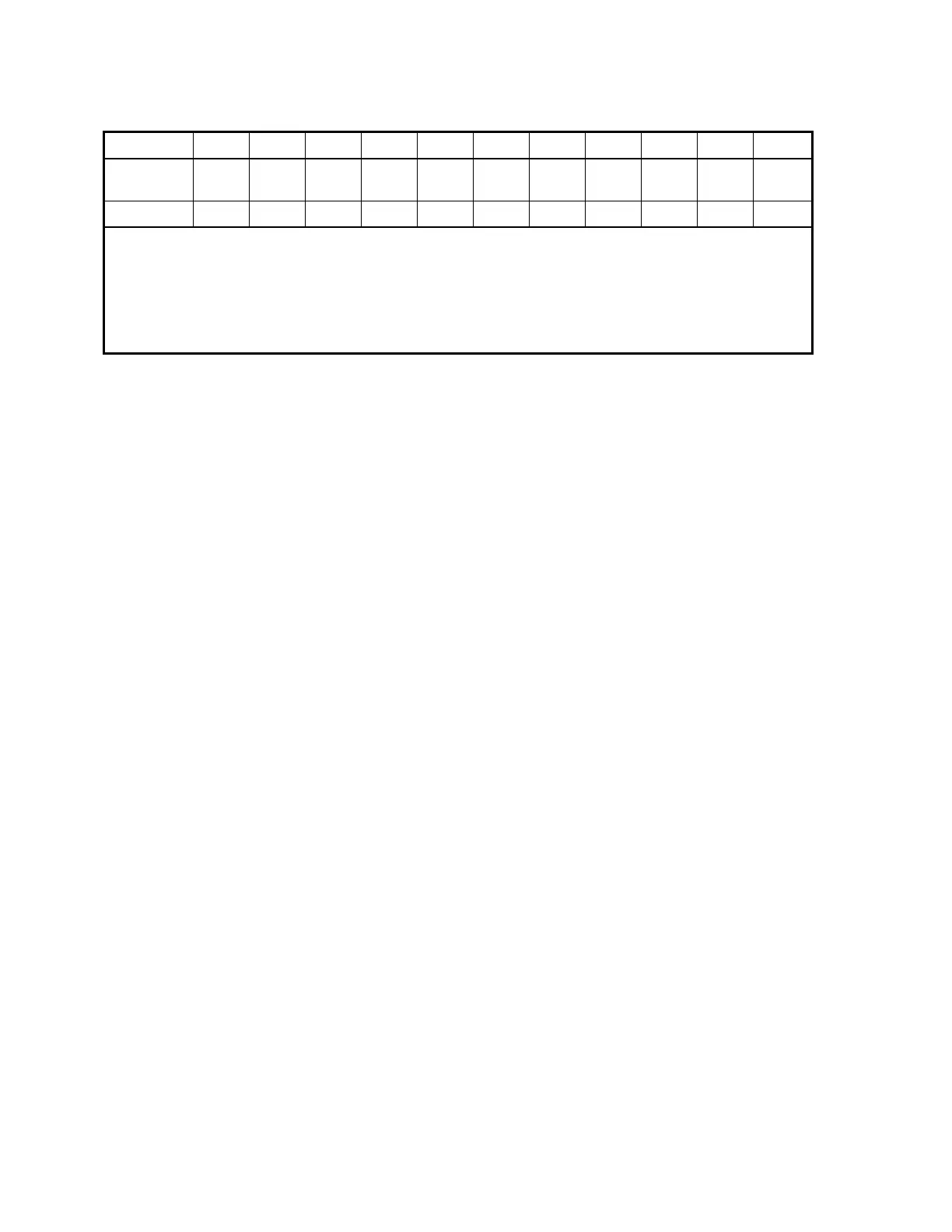

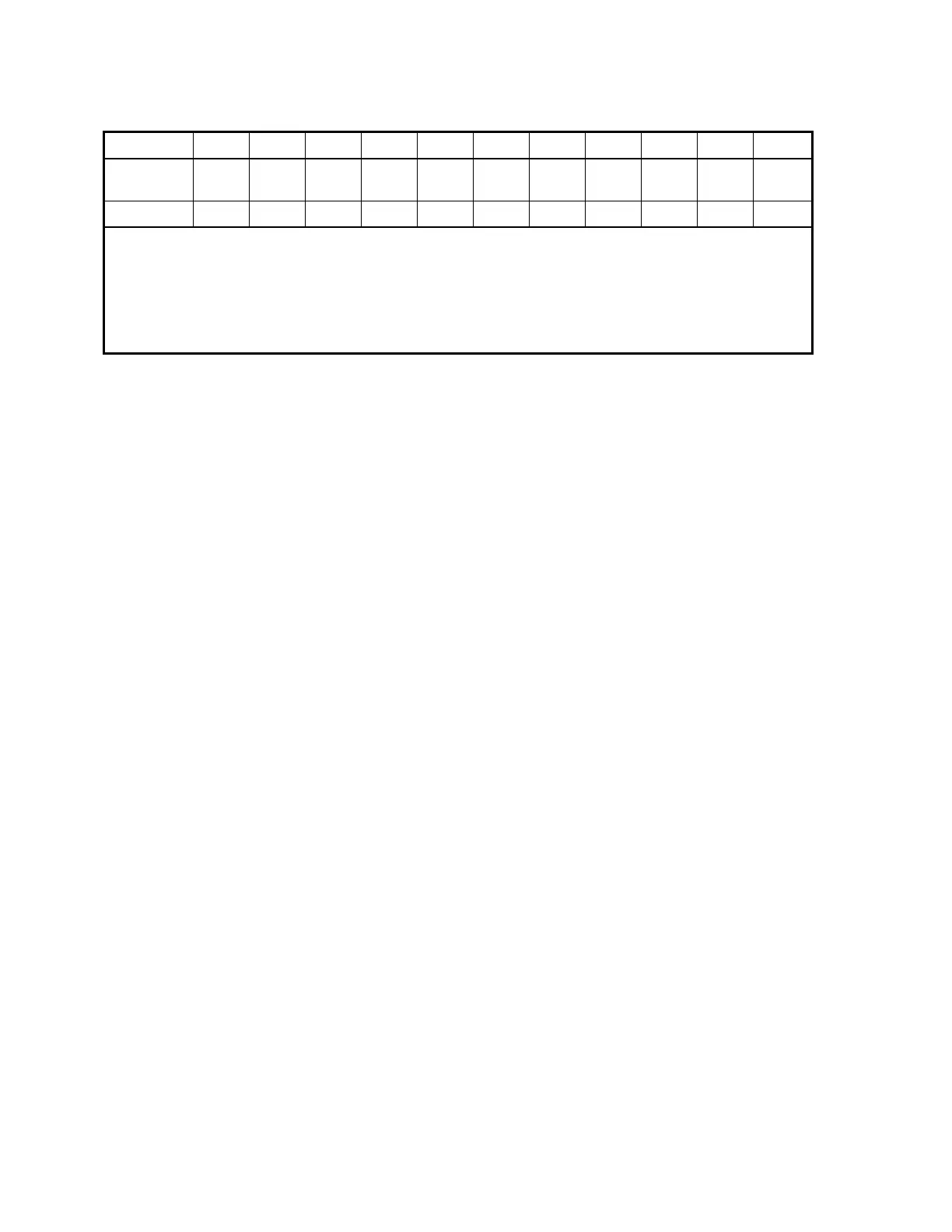

Table 4-5. Bit Configuration of Questionable Status Registers

OV = overvoltage protection has tripped

OCP = overcurrent protection has tripped

FS = the fuse is blown

OT = overtemperature protection has tripped

RI = remote inhibit is active

Unreg = output is unregulated

Meas Ovld = measurement overload

STATus:QUEStionable?

This query returns the value of the Questionable Event register. The Event register is a read-only register

which holds (latches) all events that are passed by the Questionable NTR and/or PTR filter. Reading the

Questionable Event register clears it.

STATus:QUEStionable[:EVENt]?

STAT:QUES? STATUS:QUESTIONABLE:EVENT?

*CLS STAT:QUES:ENAB

STAT:QUES:NTR STAT:QUES:PTR

STATus:QUEStionable:CONDition?

This query returns the value of the Questionable Condition register. That is a read-only register which

holds the real-time (unlatched) questionable status of the dc source.

STATus:QUEStionable:CONDition?

STAT:QUES:COND? STATUS:QUESTIONABLE:CONDITION?

STATus:QUEStionable:ENABle

This command and its query set and read the value of the Questionable Enable register. This register is a

mask for enabling specific bits from the Questionable Event register to set the questionable summary bit

(QUES) of the Status Byte register. This bit (bit 3) is the logical OR of all the Questionable Event register

bits that are enabled by the Questionable Status Enable register..

STATus:QUEStionable:ENABle<NRf>

STAT:QUES:ENAB 20 STAT:QUES:ENAB 16

STATus:QUEStionable:ENABle?

Loading...

Loading...