52

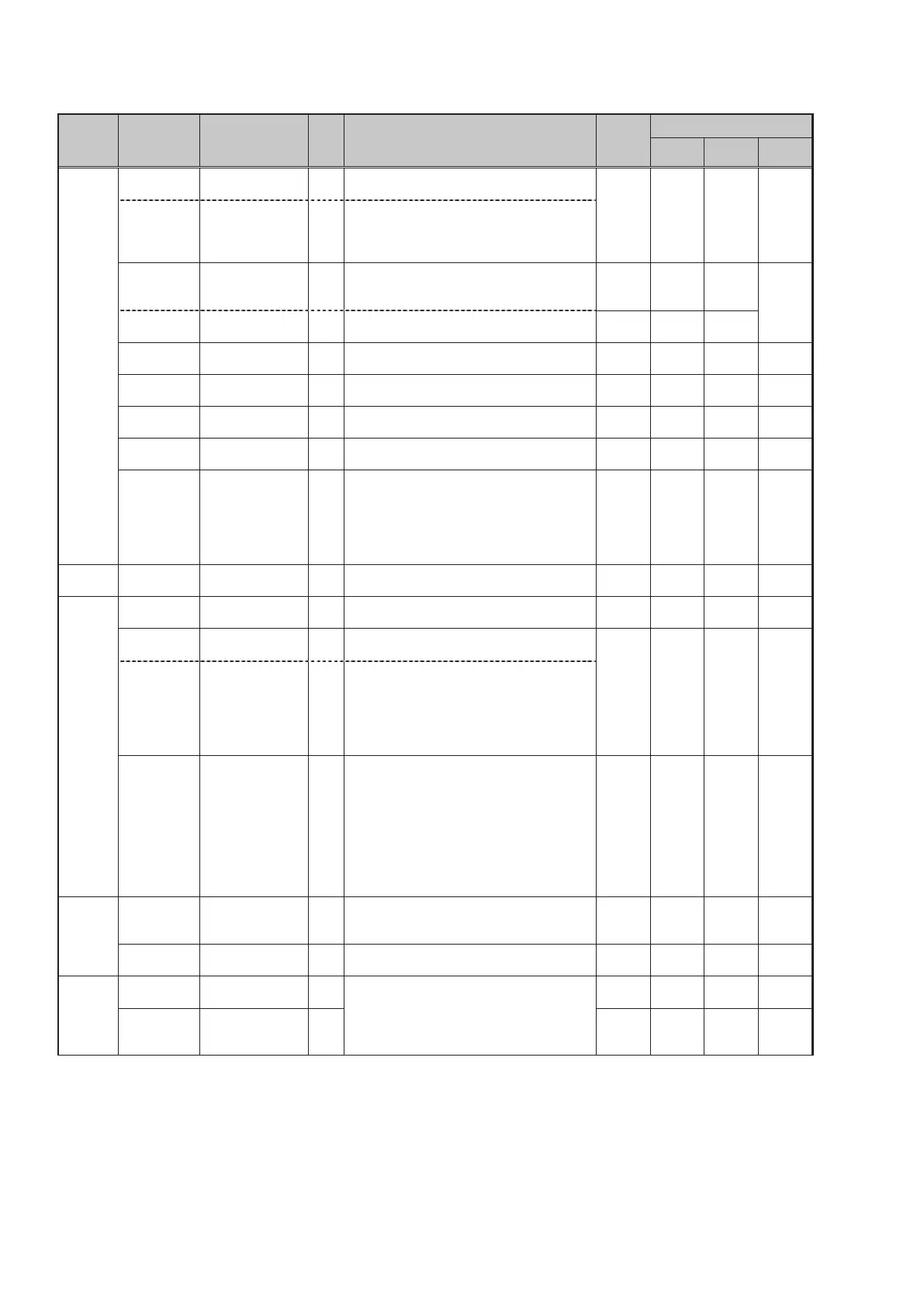

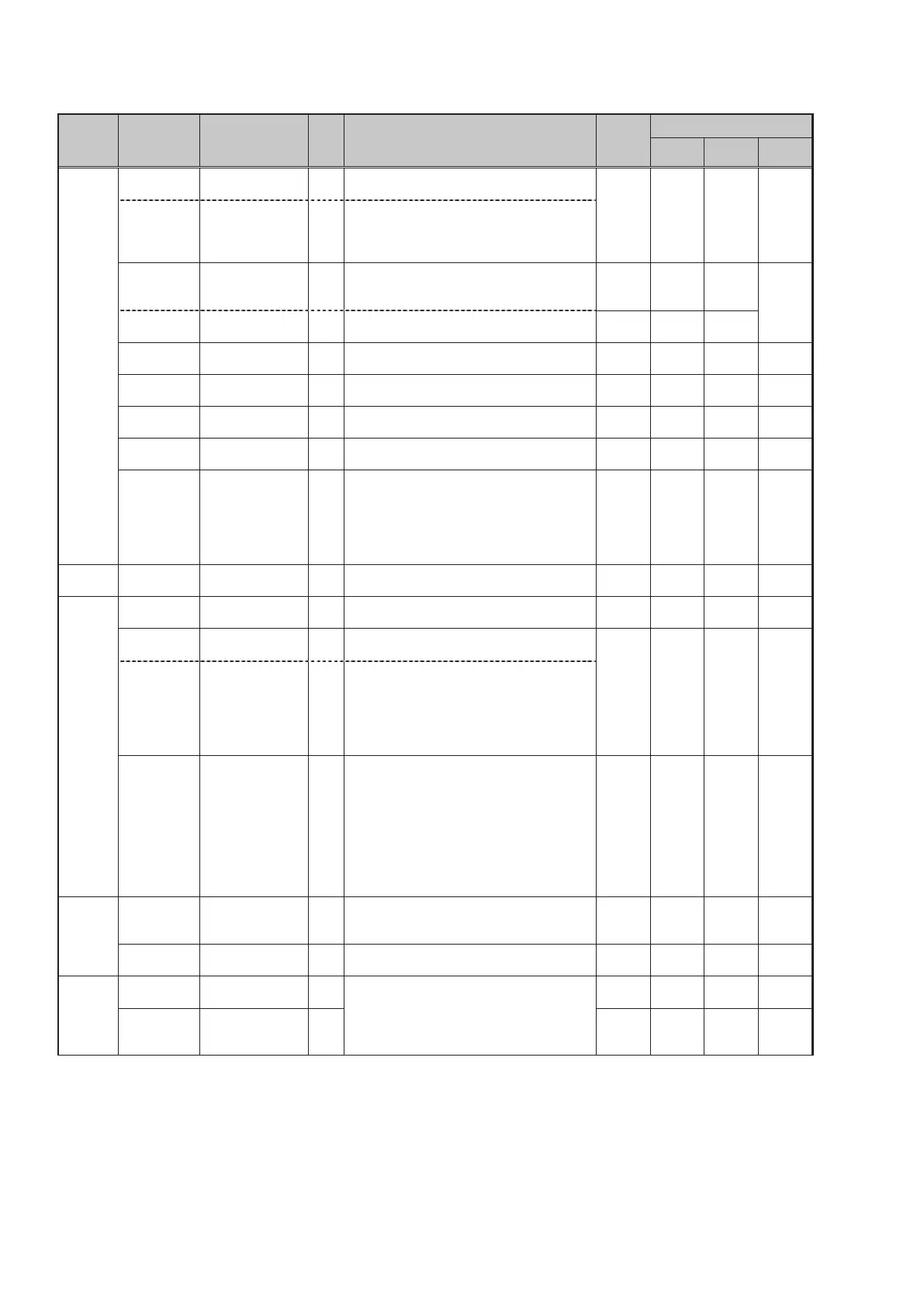

State of pin *7) Category Pin name Name I/O Function Pin

count

(Pin nos.)

RST_N=”

L”

RST_N

goes “H”

PCUT=1

D15-0 Data Bus I/O This is a 16-bit data bus. 24-39 *4) *4)

AD6-1 Multiplex

Address Bus

I/O When a multiplex bus is specified, this

group of pins is used on a time-shared

basis for some of the data buses (D6-D1),

or for 6 bits of the address bus (A6-A1).

Input

(Hi-z)

A6-1 Address Bus IN This is a 6-bit address bus.

Because the data bus consists of 16 bits,

there is no A0.

18-23 Input

*5)

Input

*5)

ALE Address Latch

Enable

IN When a multiplex bus is specified, the A6

pin is used as the ALE signal.

Input Input

Input

(Hi-z)

Input

CS_N Chip Select IN Setting this to the “L” level selects this

controller.

56 Input

*6)

Input

*6)

Input

RD_N Read Strobe IN Setting this to the “L” level reads data

from the controller registers.

53 Input Input Input

WR0_N D7-0 Byte Write

Strobe

IN At the rising edge, D7-D0 are written to

the registers of the controller.

54 Input

*6)

Input

*6)

Input

WR1_N D15-8 Byte Write

Strobe

IN At the rising edge, D15-D8 are written to

the registers of the controller.

55 Input

*6)

Input

*6)

Input

CPU bus

interface

MPBUS*3 Bus Mode

Selection

IN Setting this to the “L” level selects a

separate bus.

Setting this to the “H” level selects a

multiplex bus.

This should be fixed at either the “H” or “L”

level.

17 Input

*3)

Input

*3)

Input

*3)

Split bus

interface

SD7-0 Split Data Bus I/O If a split bus is selected, this functions as

the data bus for the split bus.

43-50 Input

(Hi-z)

Input

(Hi-z)

Input

(Hi-z)

DREQ0_N*1

DREQ1_N*1

DMA Request OUT This notifies the system of a D0FIFO port

or D1FIFO port DMA transfer request.

57, 60 H H H/L

*8)

DACK0_N*1

DACK1_N*1

DMA

Acknowledge

IN Input the DMA Acknowledge signal for the

D0FIFO or D1FIFO port.

58, 61 Input Input

DSTB0_N*2 Data Strobe 0 IN This functions as the data strobe signal

for the D0FIFO port.

Because it is also used for the DMA

Acknowledge signal of the D1FIFO port,

the DSTB0_N function cannot be used if

the DACK1_N function is being used.

Input

DMA bus

interface

DEND0_N*1

DEND1_N*1

DMA Transfer

End

I/O <In the FIFO port access writing

direction>

This receives the Transfer End signal

from another peripheral chip or the CPU

as an input signal.

<In the FIFO port access reading

direction>

This indicates the transfer end data as an

output signal.

59, 62 Input

(Hi-z)

Input

(Hi-z)

Input

(Hi-z)

INT_N Interrupt OUT In the “L” active state, this notifies the

system of various types of interrupts

relating to USB communication.

51 H H H Interrupt/

SOF

output

SOF_N SOF pulse output OUT When an SOF is detected in the “L” active

state, an SOF pulse is output.

52 H H H

10 NI tupni noitallicsO NIXClock

XOUT Oscillation output OUT

A crystal oscillator should be connected

between XIN and XOUT. When using

external clock input, the external clock

signal should be connected to XIN, and

XOUT should be open.

11

PIN DESCRIPTIONS

Loading...

Loading...