Doc. No. MV-S105540-00, Rev. A

Document Classification: Proprietary Information Page 13

Signal Description

Pin Description

The GMII interface supports both 1000BASE-T and 1000BASE-X modes of operation. The GMII interface pins are

also used for the TBI interface. See Ta b l e 3 for TBI pin definitions. The MAC interface pins are 3.3V tolerant.

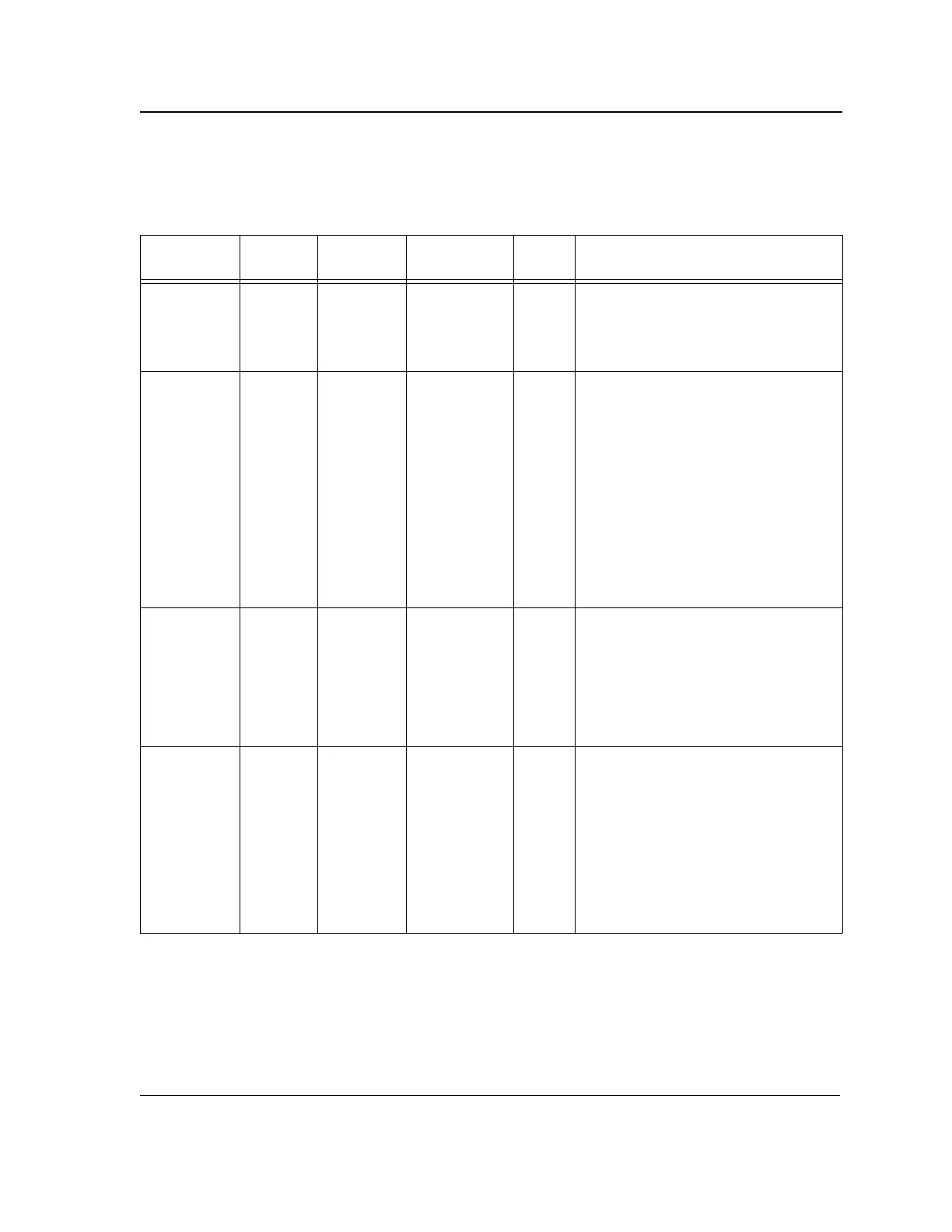

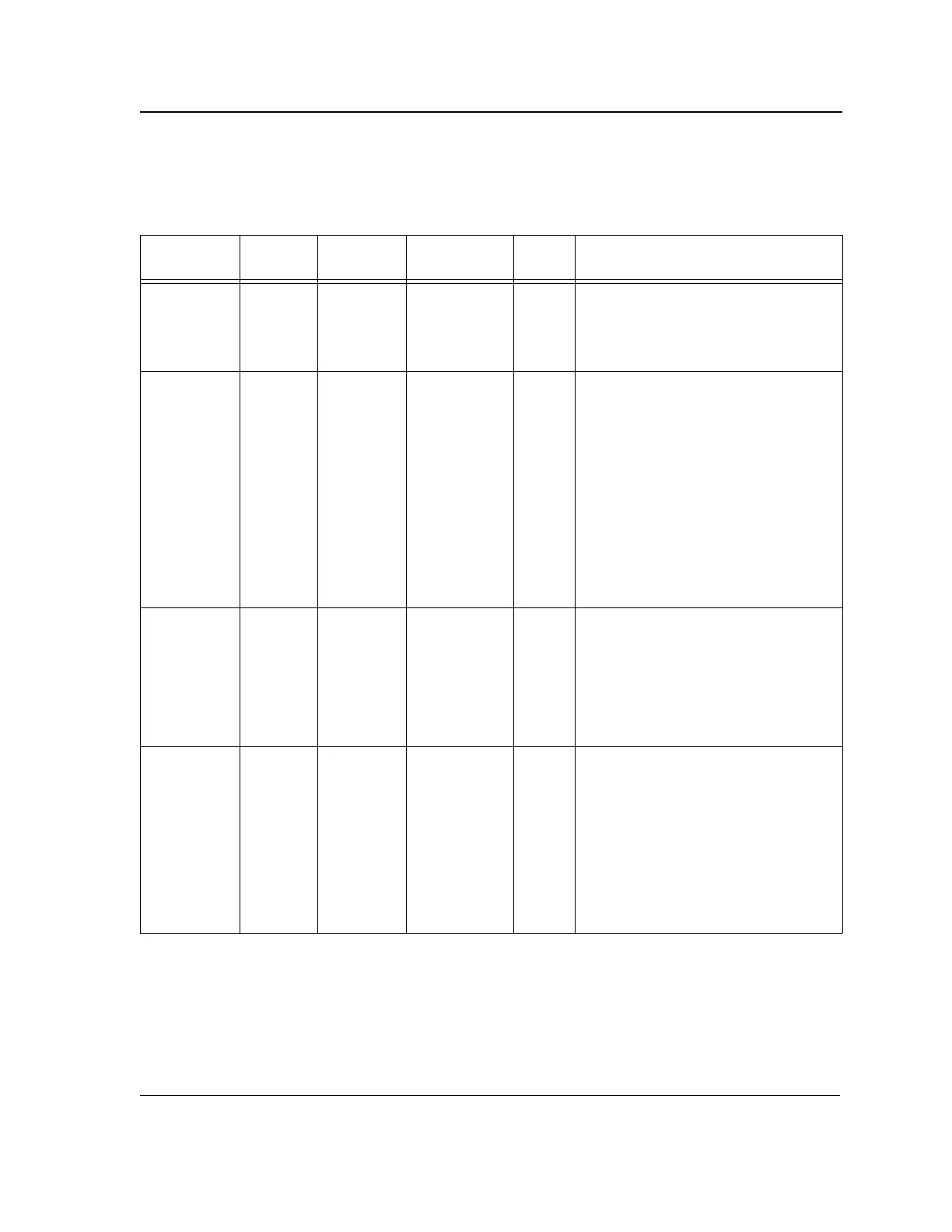

Table 2: GMII/MII Interfaces

117-TFBGA

Pin #

96-aQFN

Pin #

128-PQFP

Pin #

Pin Name Pin

Type

Description

E2 B4 14 GTX_CLK I GMII Transmit Clock. GTX_CLK provides a

125 MHz clock reference for TX_EN,

TX_ER, and TXD[7:0]. This clock can be

stopped when the device is in 10/100BASE-

T modes, and also during Auto-Negotiation.

D1 B2 10 TX_CLK O, Z MII Transmit Clock. TX_CLK provides a 25

MHz clock reference for TX_EN, TX_ER,

and TXD[3:0] in 100BASE-TX mode, and a

2.5 MHz clock reference in 10BASE-T

mode.

TX_CLK provides a 25 MHz, 2.5 MHz, or 0

MHz clock during 1000 Mbps Good Link,

Auto-Negotiation, and Link Lost states

depending on the setting of register 20.6:4.

The 2.5 MHz clock is the default rate, which

may be programmed to another frequency

by writing to register 20.6:4.

E1 A5 16 TX_EN I GMII and MII Transmit Enable. In GMII/MII

mode when TX_EN is asserted, data on

TXD[7:0] along with TX_ER is encoded and

transmitted onto the cable.

TX_EN is synchronous to GTX_CLK, and

synchronous to TX_CLK in 100BASE-TX

and 10BASE-T modes.

F2 A4 13 TX_ER I GMII and MII Transmit Error. In GMII/MII

mode when TX_ER and TX_EN are both

asserted, the transmit error symbol is trans-

mitted onto the cable. When TX_ER is

asserted with TX_EN de-asserted, carrier

extension symbol is transmitted onto the

cable.

TX_ER is synchronous to GTX_CLK, and

synchronous to TX_CLK in 100BASE-TX

and 10BASE-T modes.

Copyright © 2020 Marvell

December 2, 2020

Loading...

Loading...