Doc. No. MV-S105540-00, Rev. A

Document Classification: Proprietary Information Page 15

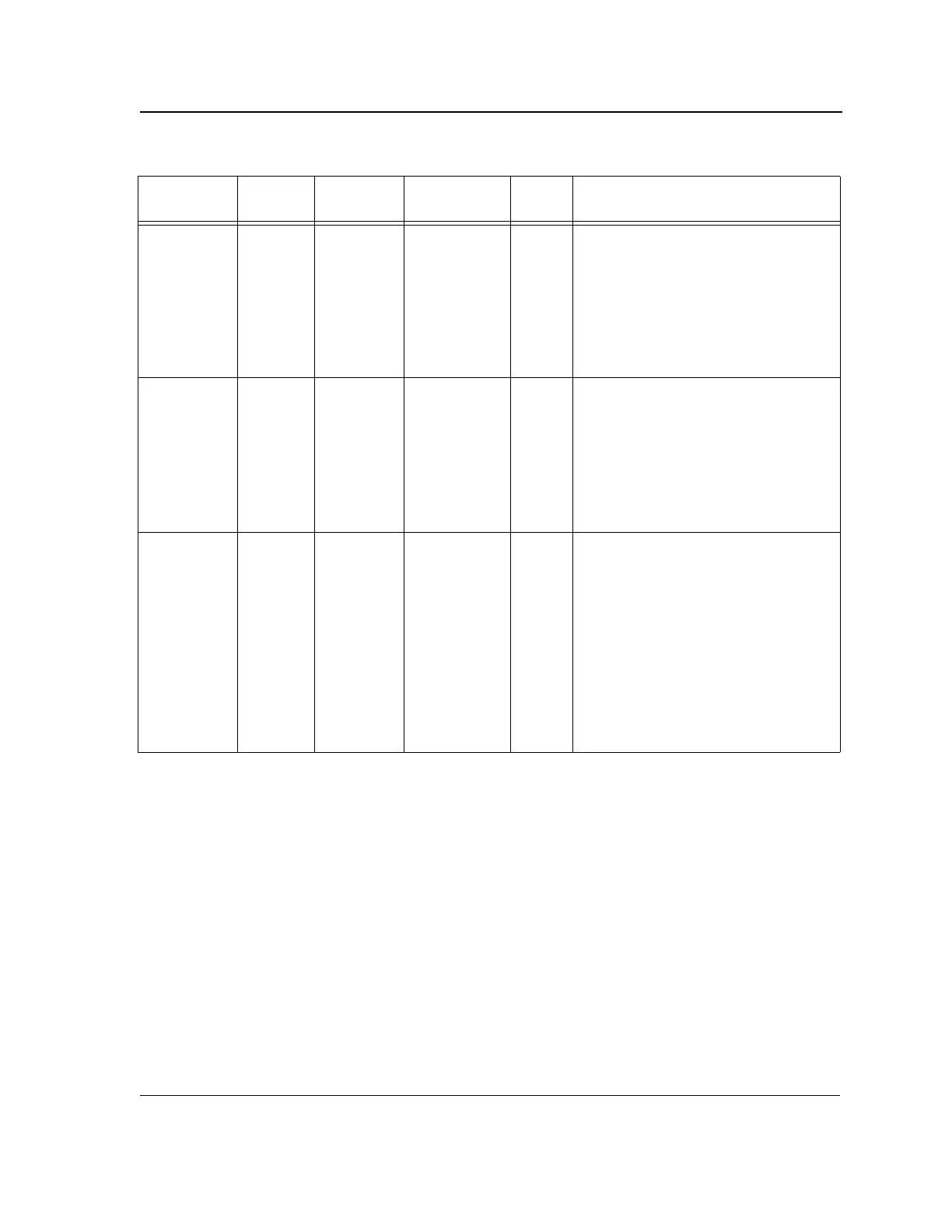

Signal Description

Pin Description

C5

A2

A1

C4

B3

C3

D3

B2

B40

A47

A48

B42

A49

A50

B43

A51

120

121

123

124

125

126

128

3

RXD[7]

RXD[6]

RXD[5]

RXD[4]

RXD[3]/RXD[3]

RXD[2]/RXD[2]

RXD[1]/RXD[1]

RXD[0]/RXD[0]

O, Z GMII and MII Receive Data. Symbols

received on the cable are decoded and pre-

sented on RXD[7:0] in 1000BASE-T mode.

In MII mode, RXD[3:0] are used in

100BASE-TX and 10BASE-T modes. In MII

mode, RXD[7:4] are driven low.

RXD[7:0] is synchronous to RX_CLK.

B5 B39 115 CRS O, Z GMII and MII Carrier Sense. CRS asserts

when the receive medium is non-idle. In half-

duplex mode, CRS is also asserted during

transmission. CRS assertion during half-

duplex transmit can be disabled by program-

ming register 16.11 to 0.

CRS is asynchronous to RX_CLK,

GTX_CLK, and TX_CLK.

B6 A45 114 COL O, Z GMII and MII Collision. In 10/100/

1000BASE-T full-duplex modes, COL is

always low. In 10/100/1000BASE-T half-

duplex modes, COL asserts only when both

the transmit and receive media are non-idle.

In 10BASE-T half-duplex mode, COL is

asserted to indicate signal quality error

(SQE). SQE can be disabled by clearing reg-

ister 16.2 to zero.

COL is asynchronous to RX_CLK,

GTX_CLK, and TX_CLK.

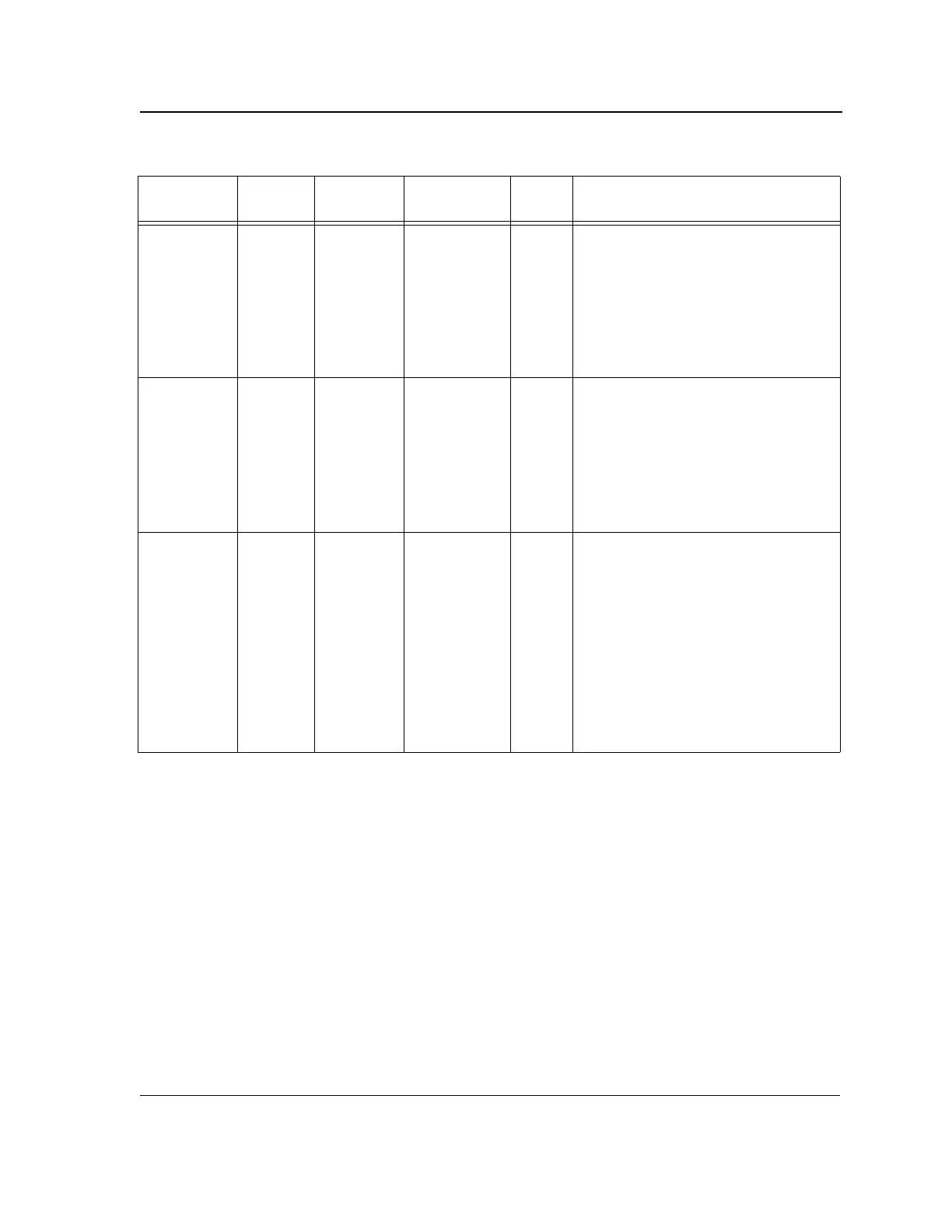

Table 2: GMII/MII Interfaces (Continued)

117-TFBGA

Pin #

96-aQFN

Pin #

128-PQFP

Pin #

Pin Name Pin

Type

Description

Copyright © 2020 Marvell

December 2, 2020

Loading...

Loading...