Doc. No. MV-S105540-00, Rev. A

Page 30 Document Classification: Proprietary Information

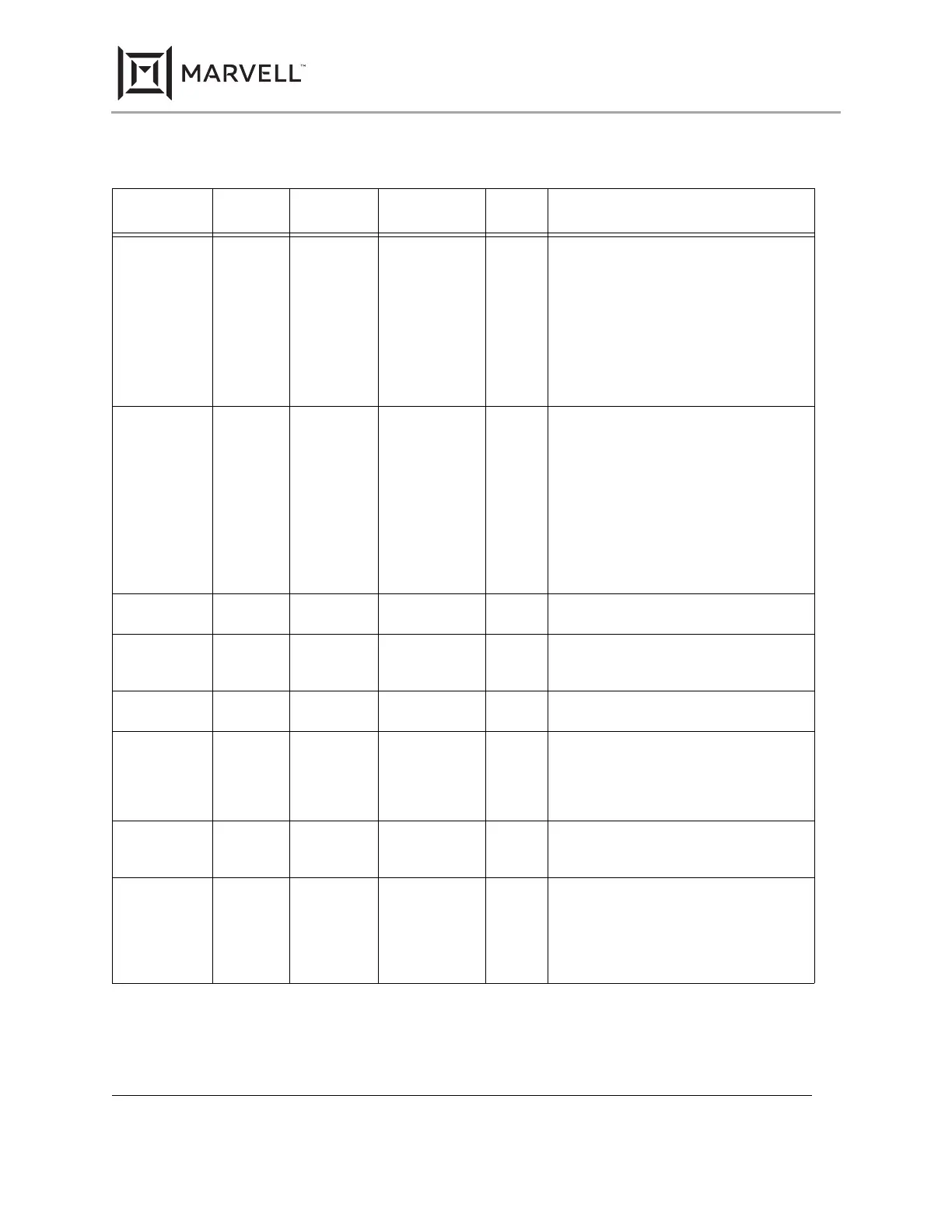

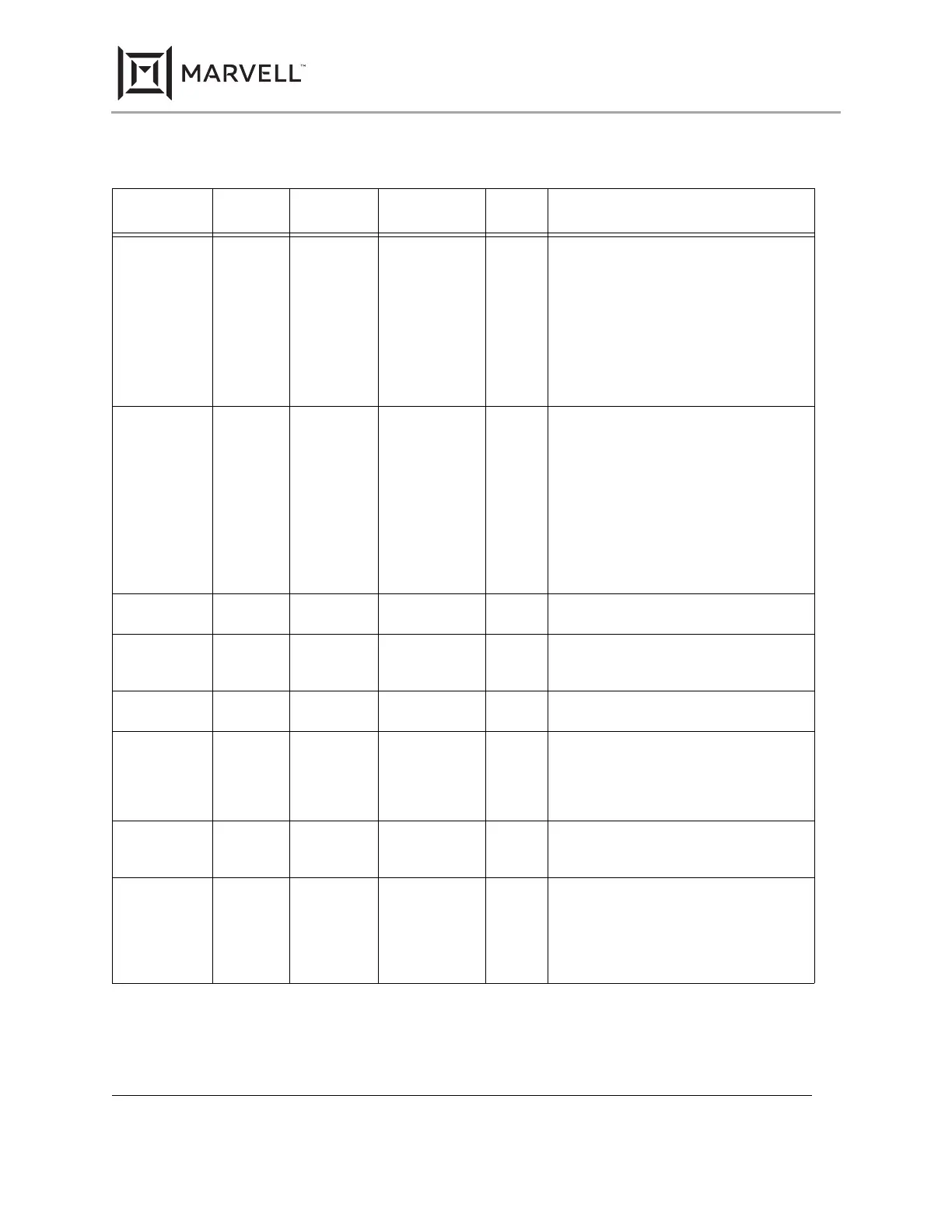

F8 A34 86 CONFIG[2] I CONFIG[2] pin configures ANEG[3:1] bits.

Each LED pin is hardwired to a constant

value. The values associated to the CON-

FIG[2] pin are latched at the de-assertion of

hardware reset.

CONFIG[2] pin must be tied to one of the

pins based on the configuration options

selected. They should not be left floating.

G7 A33 82 CONFIG[3] I CONFIG[3] pin configures ANEG[0],

ENA_XC, and DIS_125 options.

Each LED pin is hardwired to a constant

value. The values associated to the CON-

FIG[3] pin are latched at the de-assertion of

hardware reset.

CONFIG[3] pin must be tied to one of the

pins based on the configuration options

selected. They should not be left floating.

F9 B28 81 CONFIG[4] I CONFIG[4] pin configures

HWCFG_MODE[2:0] options.

G9 A32 80 CONFIG[5] I CONFIG[5] pin configures DIS_FC,

DIS_SLEEP, and HWCFG_MODE[3]

options.

G8 B27 79 CONFIG[6] I CONFIG[6] pin configures SEL_TWSI,

INT_POL, and 75/50 OHM options.

H8 B26 77 SEL_FREQ Frequency Selection for XTAL1 input

NC = Selects 25 MHz clock input.

Tied low = Selects 125 MHz clock input.

Internally divided to 25 MHz.

SEL_FREQ is internally pulled up.

H9 A30 76 XTAL1 I Reference Clock. 25 MHz ± 50 ppm or 125

MHz ± 50 ppm oscillator input. PLL clocks

are not recommended.

J9 B25 75 XTAL2 0 Reference Clock. 25 MHz ± 50 ppm toler-

ance crystal reference. When the XTAL2 pin

is not connected, it should be left floating.

There is no option for a 125 MHz crystal.

See "Crystal Oscillator" Application Note for

details.

Table 12: Clock/Configuration/Reset/I/O (Continued)

117-TFBGA

Pin #

96-aQFN

Pin #

128-PQFP

Pin #

Pin Name Pin

Type

Description

88E1111 Product Brief

Integrated 10/100/1000 Ultra Gigabit Ethernet Transceiver

Copyright © 2020 Marvell

December 2, 2020

Loading...

Loading...