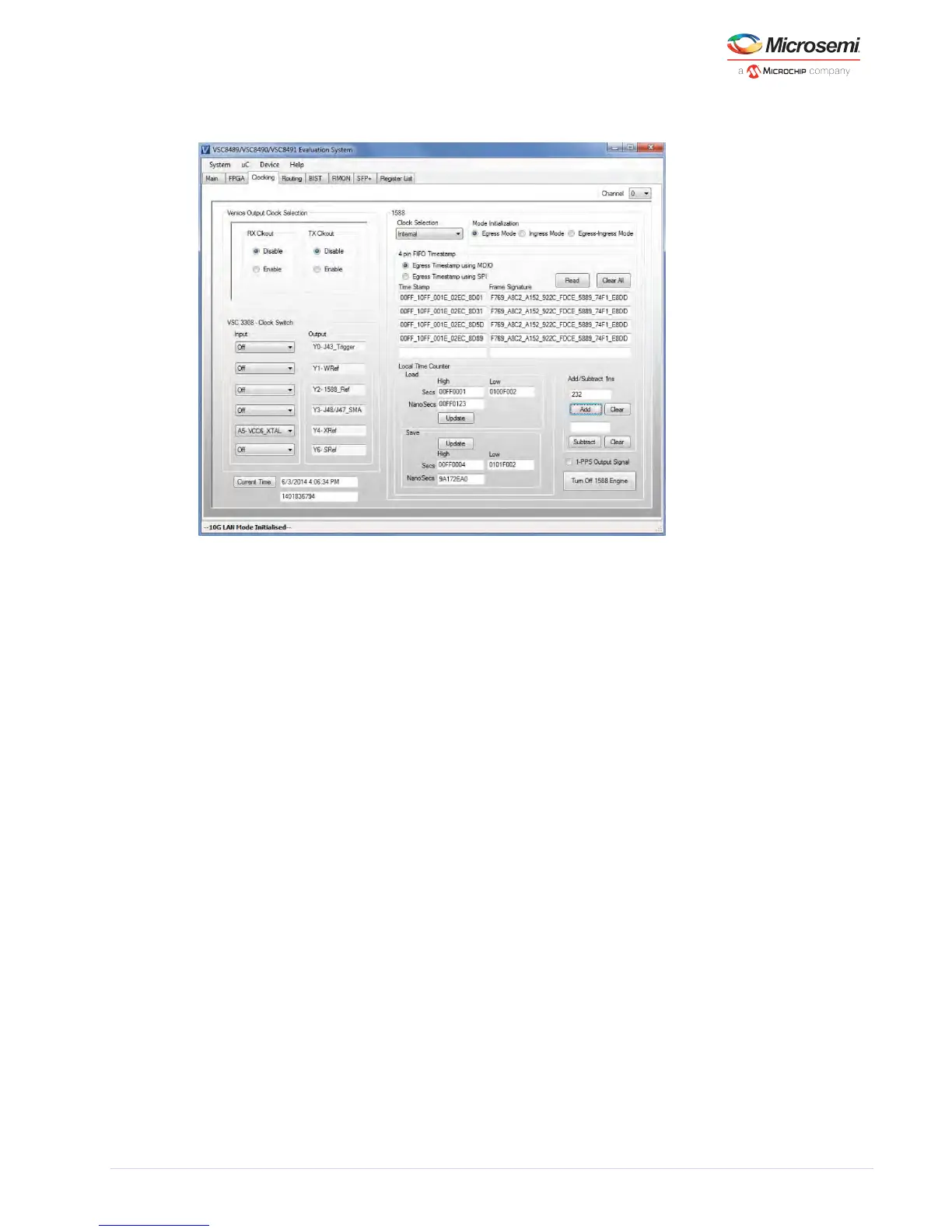

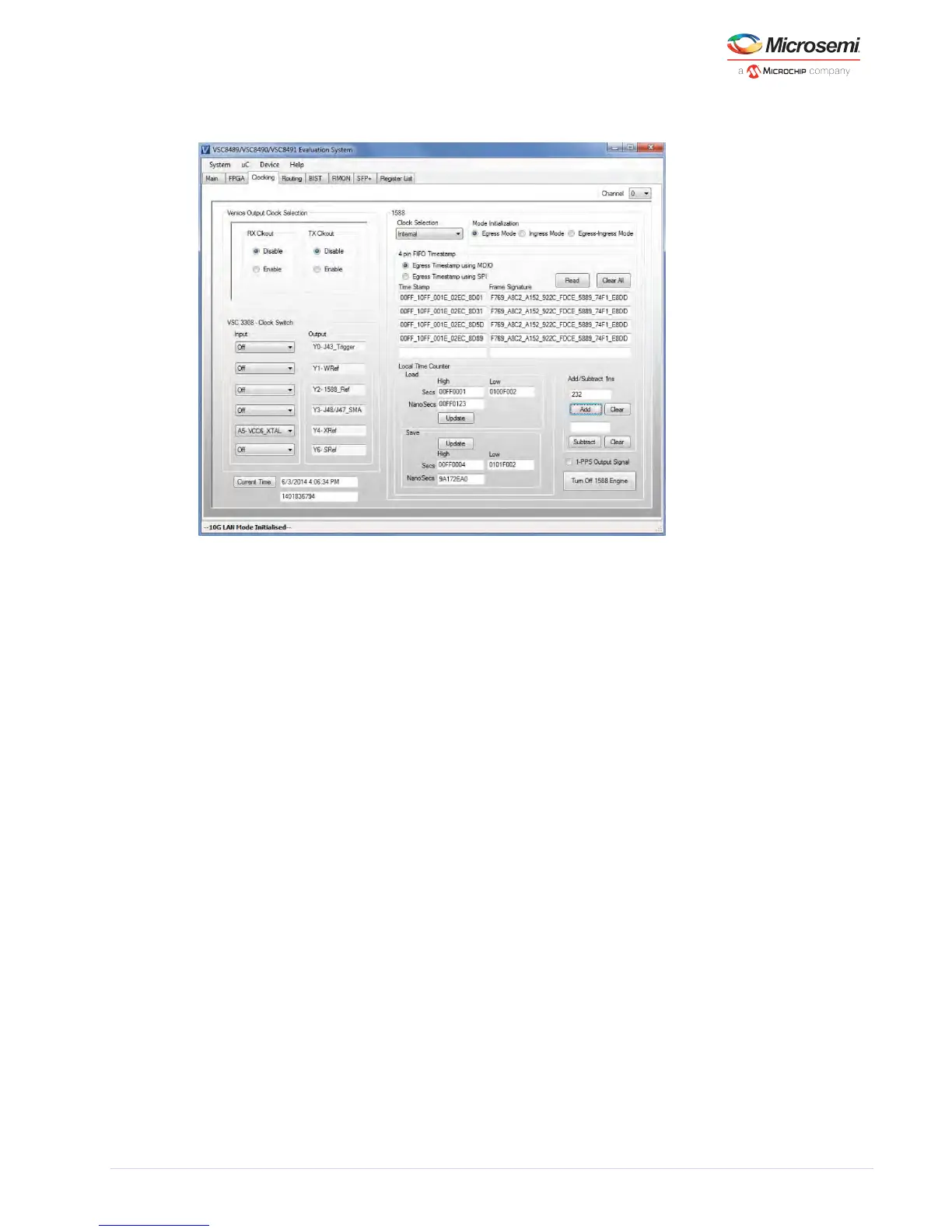

Figure 6 • GUI: Clocking Page

5.6 Routing

The Routing page controls the VSC3316 XAUI/RXAUI switch as well as device loopbacks. The Channel

Selection box in the upper right corner selects the active PHY channel to configure. A data path diagram

of the loopbacks is displayed on the top of this page.

There are 6 loopbacks and 2 BIST engines available. Three of the loopbacks are Host side loopbacks, (i.e.,

XAUI in and looped back to XAUI out). These include loopback H2, loopback H3, and loopback H4.

Loopback H2 is the shallow loopback located in the XAUI-PHY block before the 8b/10b endec. The

deeper loopback includes loopback SC8489/VSC8490/VSC8491 Evaluation Board User Guide Revision 1.0

June 2014 Vitesse Proprietary and Confidential Page 15 of 23 H3 in the PCS block right after the 64b/66b

gearbox and loopback H4 at the WIS block after the framer.

The other 3 loopbacks are line side loopbacks, (i.e., SFI in and looped back to SFI out). This includes

loopback L3, loopback L2, and loopback L1. Loopback L3 is the loopback at the PMA block while

loopback L2 is the loopback right before the data hits the XGXS block. The deepest loopback L1 is the

loopback after the 8b/10b endec. When using loopback L1 with an external 10G tester, the entire chip is

exercised with the exception of the XAUI input and output buffers.

The GUI allows the user to turn on Host and Line Side loopbacks for 10G LAN and 1G LAN modes.

Checking the box enables the loopback while un-checking disables it. Figure 7 shows L2 loopback as

turned on.

The evaluation board also supports looping back the data at the external XAUI bus. This could be looped

back to the same channel or across the two channels of the PHY. Selecting the XAUI_Rx_0 from

XAUI_Tx_0 is a same channel self loopback. Selecting the XAUI_Rx_0 from XAUI_Tx_1, and XAUI_Rx_1

from XAUI_Tx_0 at the same time, is a cross channel loopback.

Loading...

Loading...