4-39

OEP-3 V1 (UC)

4-4. Circuit Operation Description of SY-282 and IF-767 Boards

Contents

. Address map

. Circuit operation

. Communication with other boards in unit

. VPR (analog video block) control

. RS communication control

Address map

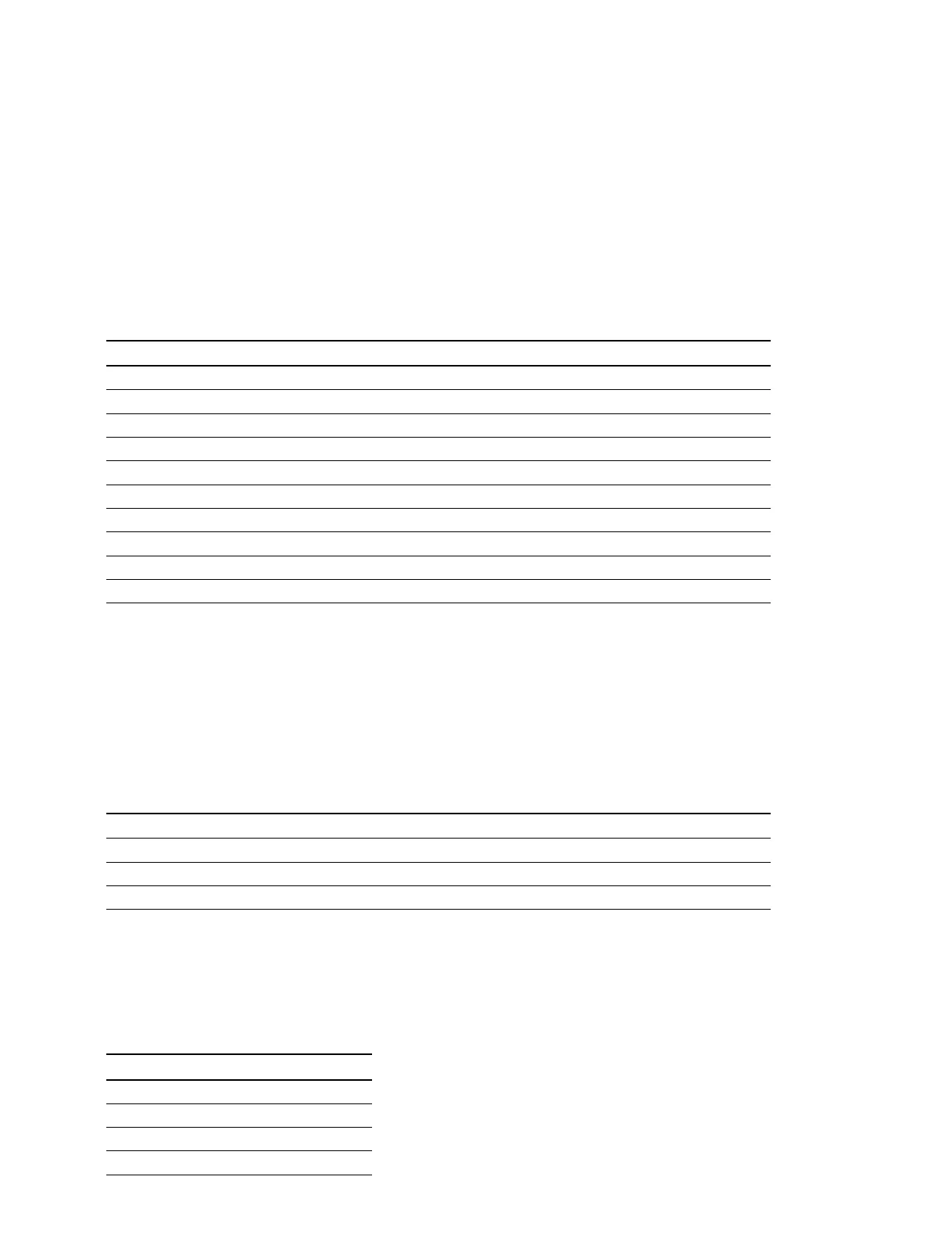

Address Contents IC CS Remarks

00000h to 3ffffh 256k-byte UV-EPROM IC200 0 & 1

2

60000h to 60003h LCD IC230 3

80000h to 81fffh 16k-byte EEPROM IC220 4

A0000h to A0001 SCI IC250 5

C0000h Expansion port IC408 6

FF710h to FFF0Fh 2k-byte SRAM IC100 CPU built-in

FFF10h to FFF13 Main and operation keys IC270 7

FFF17h REMOTE3 IC407 7

FFF1Ch to FFFFFh I/O IC100 CPU built-in

4-4-1. Circuit Operation

Reset circuit

The reset circuit uses PST572CMT (IC190). This circuit outputs a low pulse of about 60 msec when Vcc

becomes less than 4.5 V during the power-on or off sequence. The reset pulse is input to the reset pin

(pin 63) of CPU (IC100). The CPU on the SY-282 board is then reset. After the reset is released, the

CPU outputs the reset pulses for other boards from the reset output pins (pins 59 and 60).

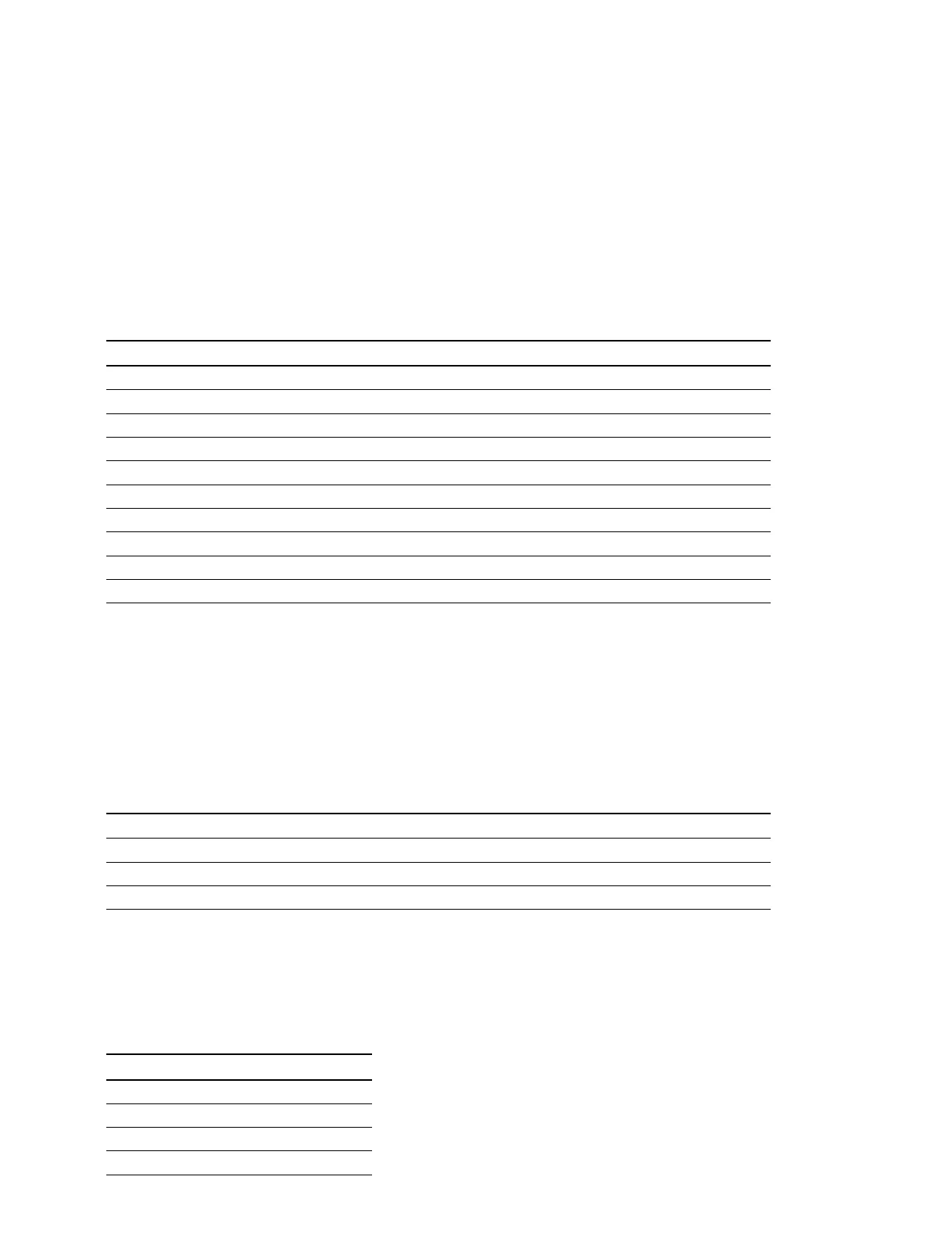

C100 TP Object to be reset Remarks

Pin 63 TP953:RESET1 CPU on SY board Output of reset circuit

Pin 59 TP594:RESET2 VPR board and peripheral circuit on SY board

Pin 60 TP596:RESET PRT board

Oscillator circuit

The basic clock (9.8304 MHz) of the SY-282 board that is generated using an oscillator circuit

incorporating a crystal oscillator (X100) and CPU (IC100) can be confirmed at pin 61 [TP955 CLOCK]

of IC100. The clock and frequency-divided clock [TP951 SCI-CLK] are sent to a serial communication

circuit (IC250). The frequency-divided clock varies depending on the baud rate setting.

Baud rate [TP951 SCI-CLK]

1200 19.2 kHz

2400 38.4 kHz

4800 76.8 kHz

9600 153.6 kHz

Loading...

Loading...