40

Appendices

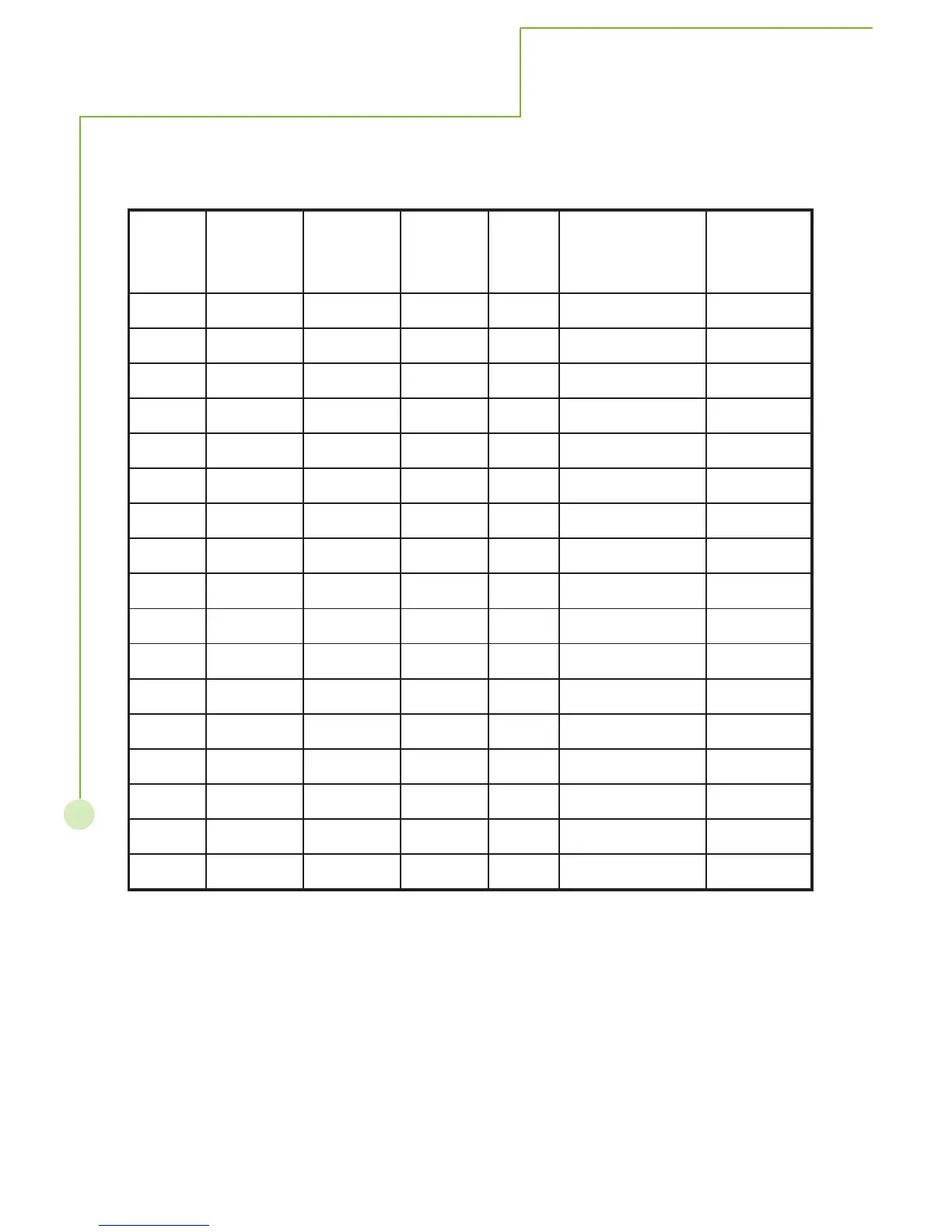

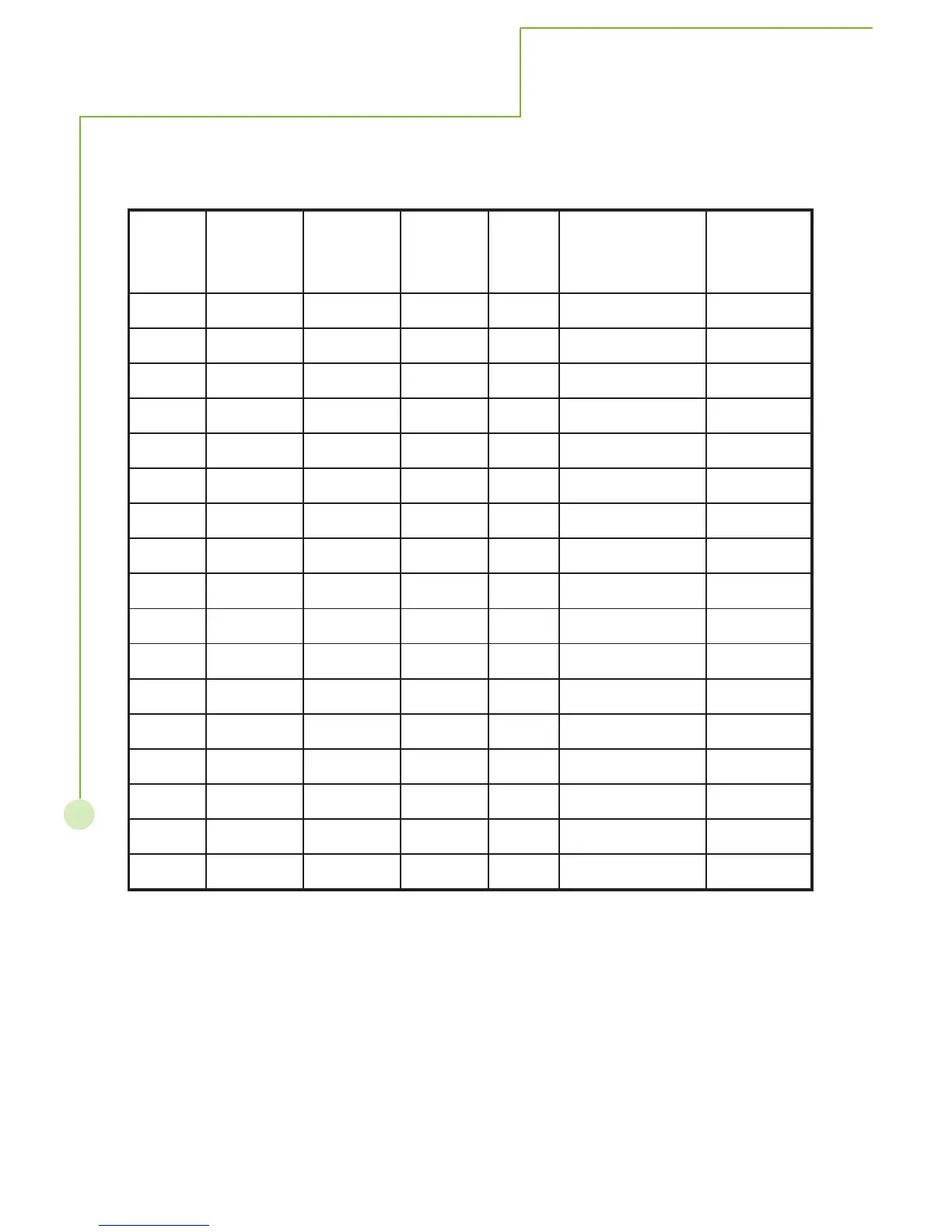

VESA Monitor Timing Spec

* The signal has been resized to meet panel’s true resolution; some detail information

might be lost during this process.

** These two modes are made possible to display by down sampling the original

analog signal. Some detail information might be lost during this process and might

cause some artifacts.

dradnatSnoituloseRetarhserfeR

)zH(

latnoziroH

ycneuqerF

)zHK(

lexiP

etar

)zHM(

golanAlatigiD

AGV084x046065.1381.52Y Y

279.7305.13YY

575.7305.13YY

583.3400.63Y Y

AGVS006x008651.5300.63Y Y

069.7300.04YY

271.8400.05Y Y

579.6405.94YY

587.3552.65YY

AGX867x4201064.8400.56Y Y

075.6500.57YY

570.0657.87YY

587.8605.49YY

AGXS4201x0821060.4600.801)sserpmoc(Y*

sserpmoc(Y*

570.0800.531)sserpmoc(Y*N

580.1905.751Y**)gnilpmasnwod(N

AGXU0021x0061060.5700.261Y**)gnilpmasnwod(N

Loading...

Loading...