LPWA Module Series

BG77 Hardware Design

BG77_Hardware_Design 28 / 76

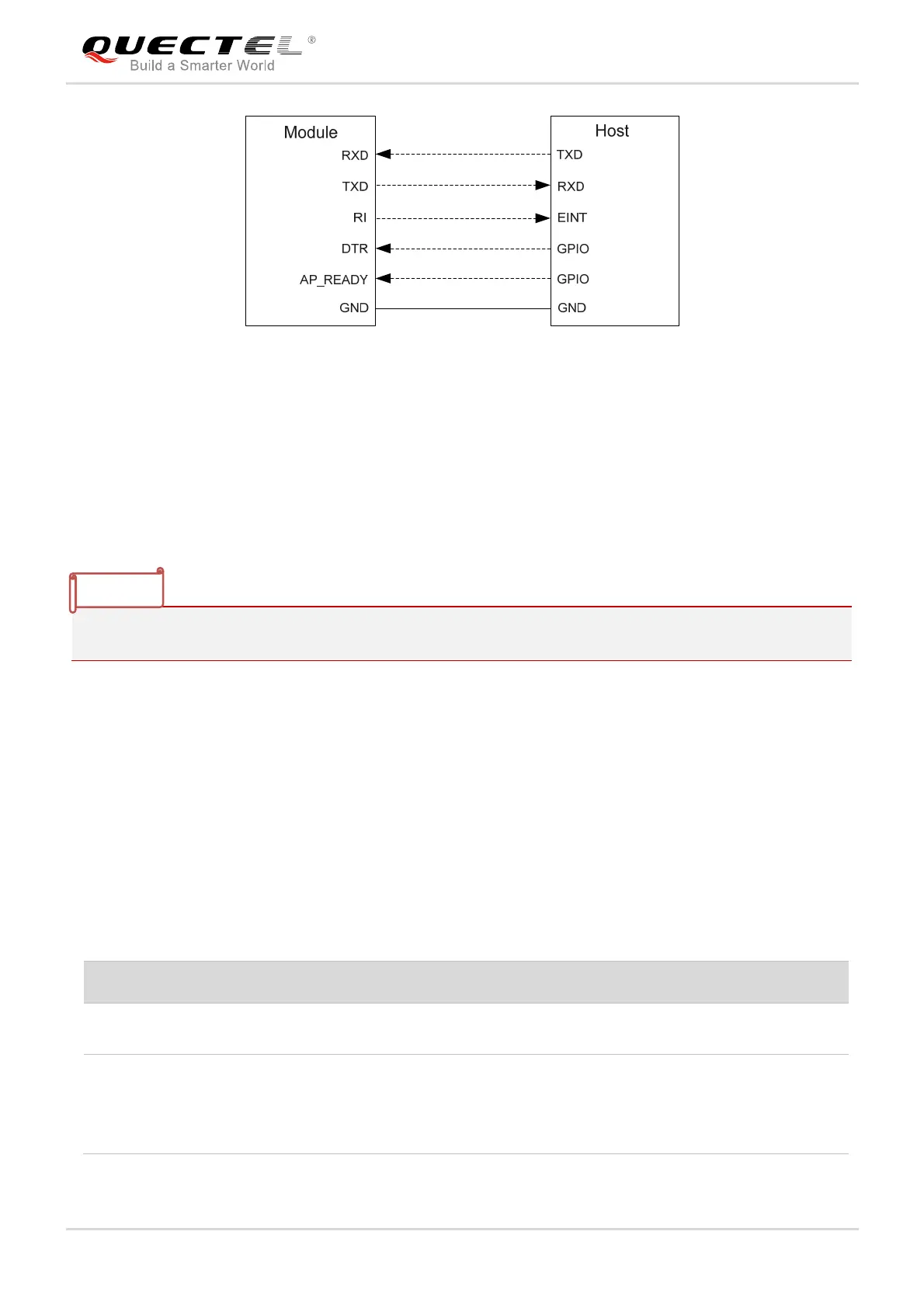

Figure 3: Sleep Mode Application via UART

When BG77 has URC to report, RI signal will wake up the host. Please refer to Chapter 3.14 for

details about RI behavior.

Driving the host DTR to low level will wake up the module.

AP_READY will detect the sleep state of the host (can be configured to high level or low level

detection). Please refer to AT+QCFG="apready" command in document [2] for details.

AP_READY function is still under development.

3.5. Power Supply

3.5.1. Power Supply Pins

BG77 provides two VBAT pins for connection with an external power supply.

The following table shows the details of VBAT pins and ground pins.

Table 6: VBAT and GND Pins

Pin Name Pin No. Description Min. Typ. Max. Unit

VBAT 19, 20

Power supply for the

module

2.6 3.3 4.8 V

GND

22~25, 27, 28, 30,

31, 47, 52~56, 58,

66, 73~75, 84~86,

88, 89

Ground - - - -

NOTE

Loading...

Loading...