57

02 is used as the write data pulse on nominal

(EARLY = 0 LATE = 0). 01 is used for the early, and

03 is used for the late. The leading edge of 04 resets

the STB line in anticipation of the next write data

pulse. When TG43 = 0 or DDEN* = 1,

precompensation is disabled and any transitions on

the WDIN line will appear on the WDOUT line.

When VFOE*/WF and WG are low, the Clock

Recovery circuits are enabled. When the RDD* line

goes low, the PU or PD* signals will become active. If

the RDD* has made its transition in the beginning of

the RCLK window, PU will go from a high impedence

state to a logic one, requesting an increase in VCO

frequency. If the RDD* line has made it transition at

the end of the RCLK window, PU will remain in the

high impedence state while PD* will go to a logic

zero, requesting a decrease in the VCO frequency.

When the leading edge of RDD* occurs in the center

of the RCLK window, both PU and PD* will remain in

the high impedence state, indicating that no

adjustment of the VCO frequency is required. By

tying PU and PD* together, an adjustment signal is

created which will be forced low for a decrease in

VCO frequency and forced high for an increase in

VCO frequency. To speed up rise times and stabilize

the output voltage, a resistor divider using R7, R10,

and R9 is used to adjust the tri-state level at

approximately 1.4V. This adjustment results in a

worst case voltage swing of plus or minus 1V, which

is acceptable for the frequency control input of the

VCO (U14). This signal derived from the combination

of PU and PD* will eventually correct the VCO input

to exactly the same frequency multiple as the FDD*

signal. The leading edge of the RDD* signal will then

occur in the exact center of the RCLK window, an

ideal condition for the 1793 internal recovery circuits.

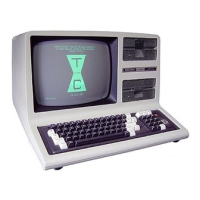

4.1.10 Floppy Disk Controller Chip

The 1793 is an MOS LSI device which performs the

functions of a floppy disk formatter/controller in a

single chip implementation. The 1793 is functionally

identical to the 1791 used on the Model II FDC

Printer Interface Board, except that the data bus is

true as opposed to inverted. Refer to the appendix

section for more information on the FD1793. The

Model II Technical Reference Manual also contains a

good presentation of the 1791 FDC chip as well as a

discussion on Write Precompensation. The following

port addresses are assigned to the internal registers

of the 1793 FDC chip.

PORT# FUNCTION

F0H Command/Status Register

F1H Track Register

F2H Sector Register

F3H Data Register

Table 4.2 Port Allocation

4.1.11 Adjustments and Jumper Options

The Data Separator must be adjusted with the 1793

in an idle condition (no command currently in

operation). Adjust R7 potentiometer for a 1.4V level

on pin 2 of U14. Then adjust R6 potentiometer to

yield a 2MHz square wave at pin l6 of U11.

The Write Precompensation must be adjusted while

executing a continuous write command on a track

greater than twenty-one. Adjust R5 potentiometer to

yield 200nsec wide pulses at pin 4 of U11. This

results in a write precompensation value of 200nsec.

There are four jumper options on the Floppy Disk

Controller Board. They are designated on the PC

Board silkscreen and are referenced on the

Schematic Diagram. The jumpers should be installed

as described below.

JUMPER CONNECTIONS

A to B

E to G

L to M

H to J

Loading...

Loading...