Renesas RA Family RA4 Quick Design Guide

R01AN5988EU0100 Rev.1.00 Page 25 of 51

Jul.21.21

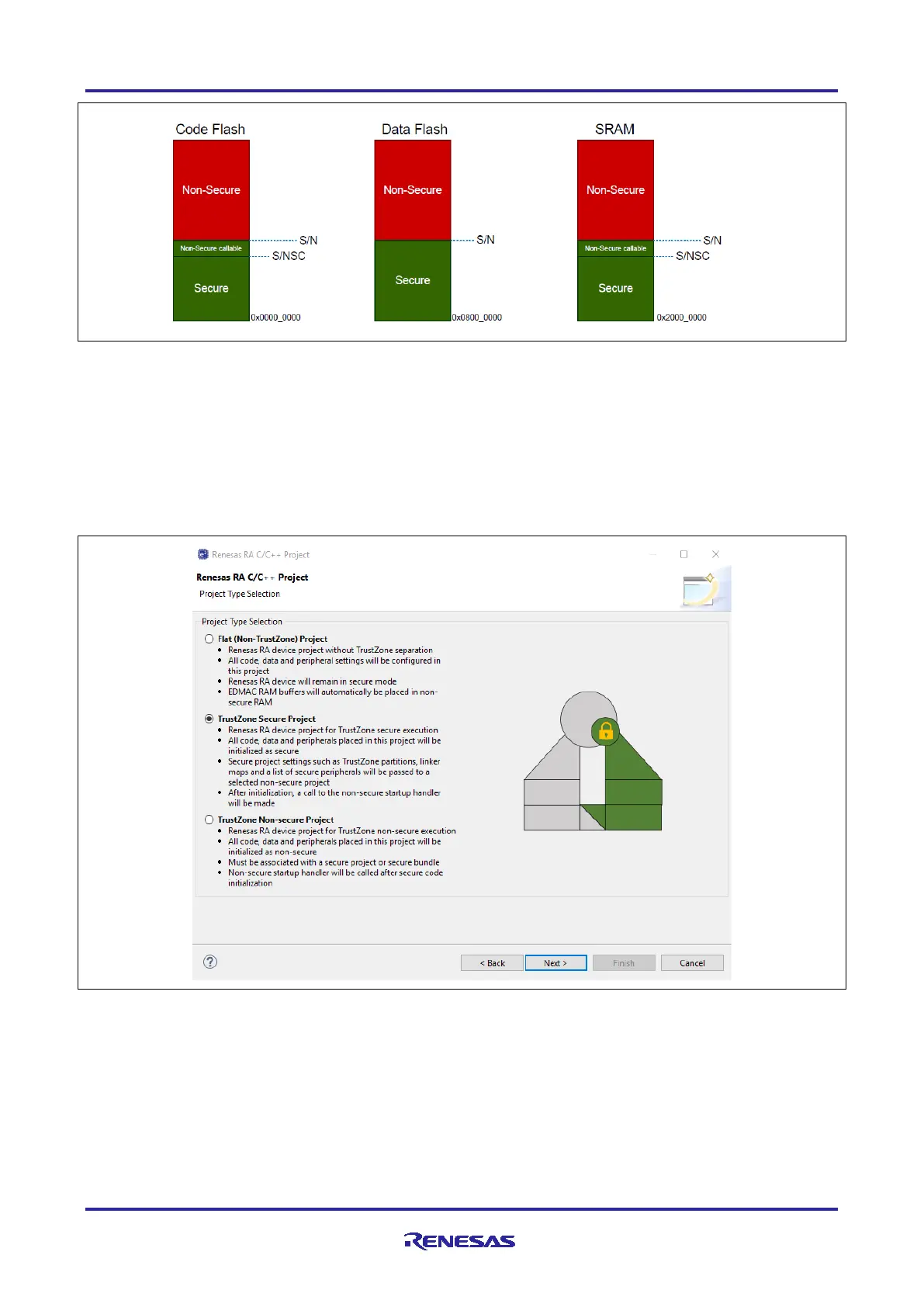

Figure 16. Secure and Non-Secure Regions

Note: All external memory accesses are considered to be Non-Secure.

Code Flash and SRAM can be divided into Secure, Non-Secure, and Non-Secure Callable. All secure

memory accesses from the Non-Secure region MUST go through the Non-Secure Callable gateway and

target a specific Secure Gateway (SG) assembler instruction. This forces access to Secure APIs at a fixed

location and prevents calls to sub-functions and so on. Failing to target an SG instruction will generate a TZ

exception. TZ enabled compilers will manage generation of the NSC veneer automatically using CMSE

extensions. These Secure, Non-Secure, and Non-Secure Callable memory regions are easily configured and

managed using FSP.

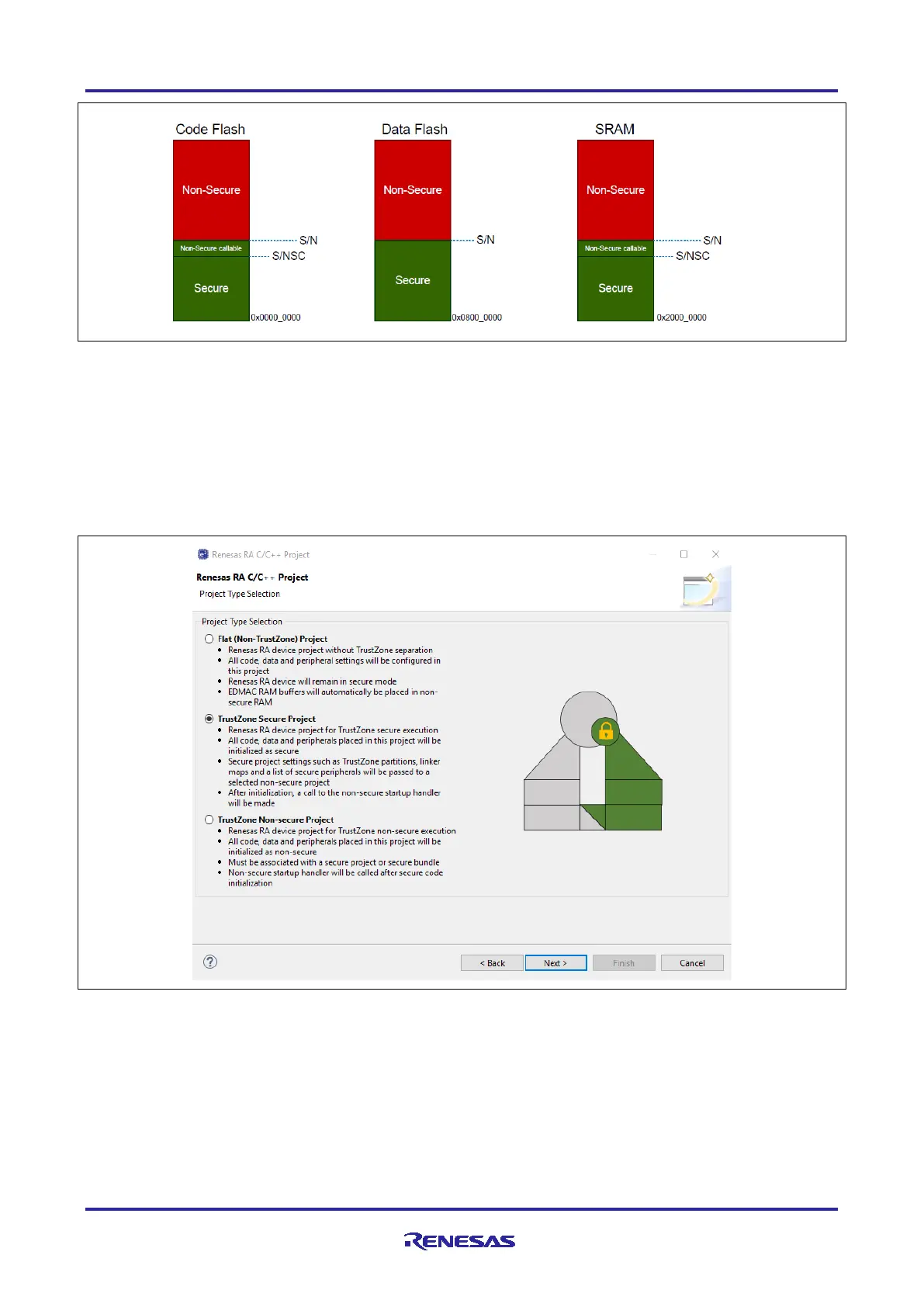

Figure 17. Using the RA Project Generator to Set Up New TZ Enabled Projects

Loading...

Loading...