Renesas RA Family RA4 Quick Design Guide

R01AN5988EU0100 Rev.1.00 Page 34 of 51

Jul.21.21

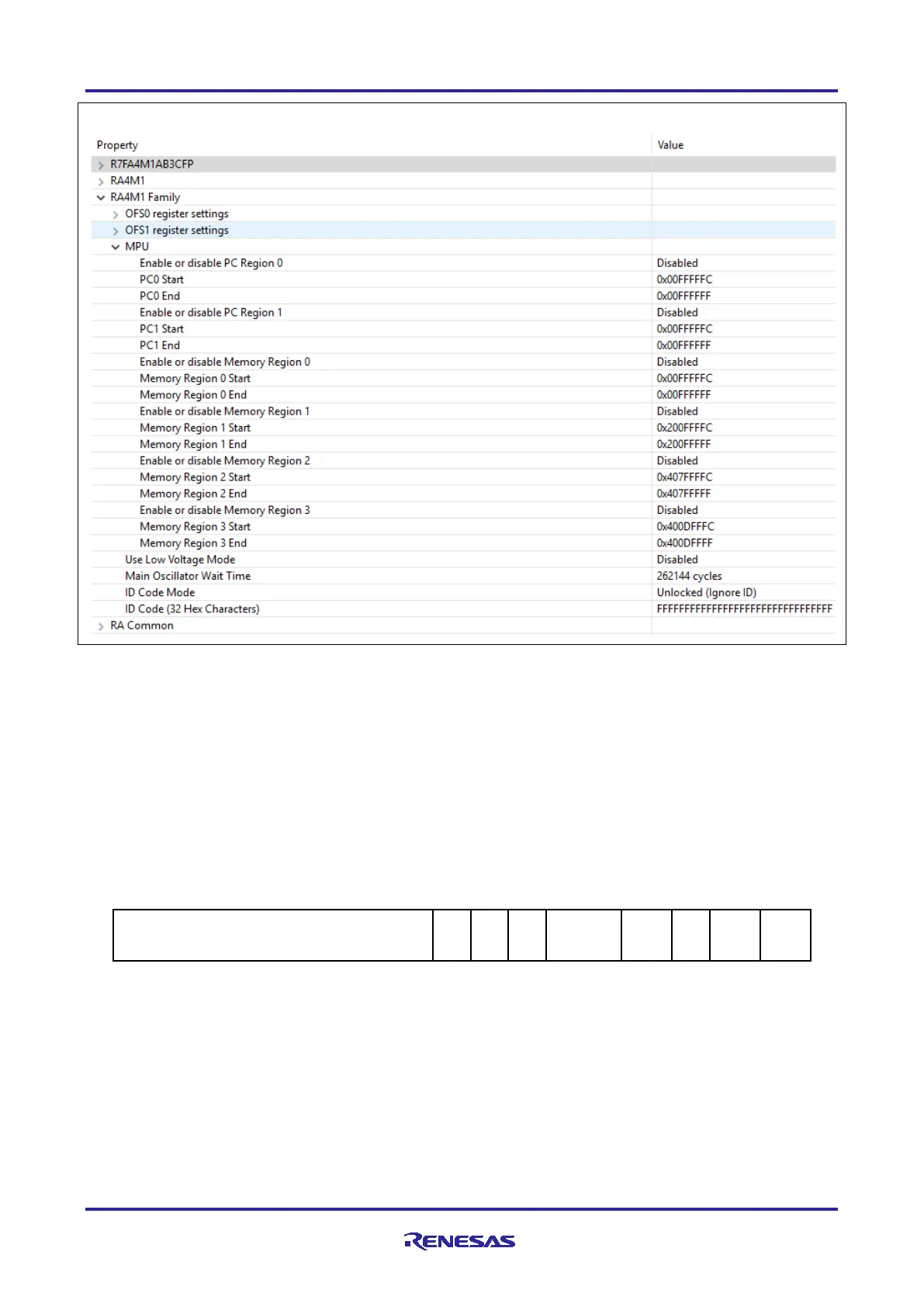

Figure 26. MPU Setup for RA4M1 (Arm Cortex-M4 core) Using Renesas FSP Configurator

Note: MPU settings must be handled carefully to prevent mistakes that may result in blocking accesses to

an MCU region.

8.5 Restriction on Endianness

Memory space containing instruction codes must be little-endian to execute code on the Arm Cortex-M core.

9. Register Write Protection

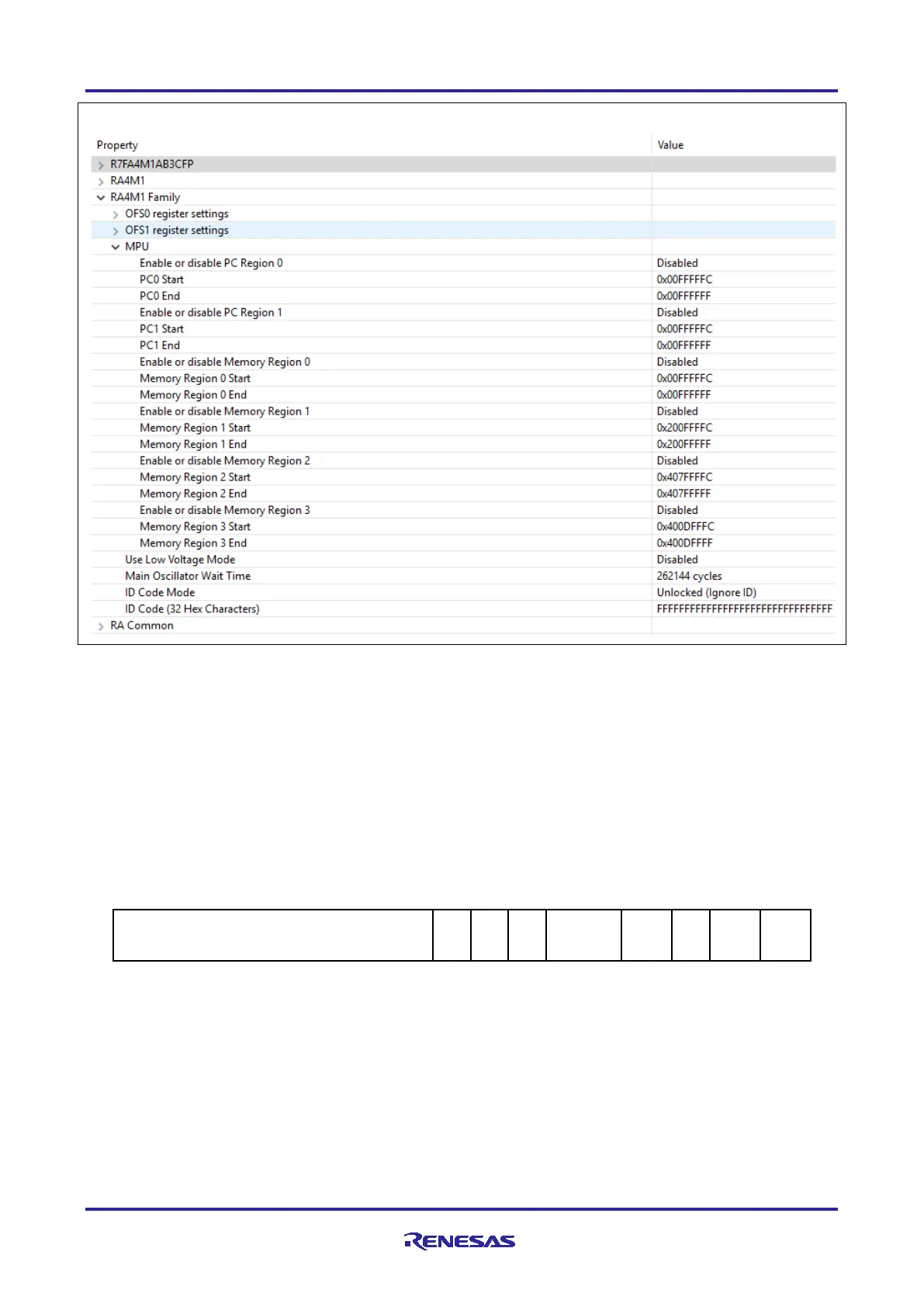

The register write protection function protects important registers from being overwritten because of software

errors. The registers to be protected are set with the Protect Register (PRCR). Table 14 lists the association

between the PRCR bits and the registers to be protected.

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

PRKEY[7:0] — — —

PRC4

*1

—

PRC3

— PRC1

PRC0

Figure 27. PRCR Register

Note 1. Not present on Arm Cortex-M4 devices.

Loading...

Loading...