Renesas RA Family RA4 Quick Design Guide

R01AN5988EU0100 Rev.1.00 Page 32 of 51

Jul.21.21

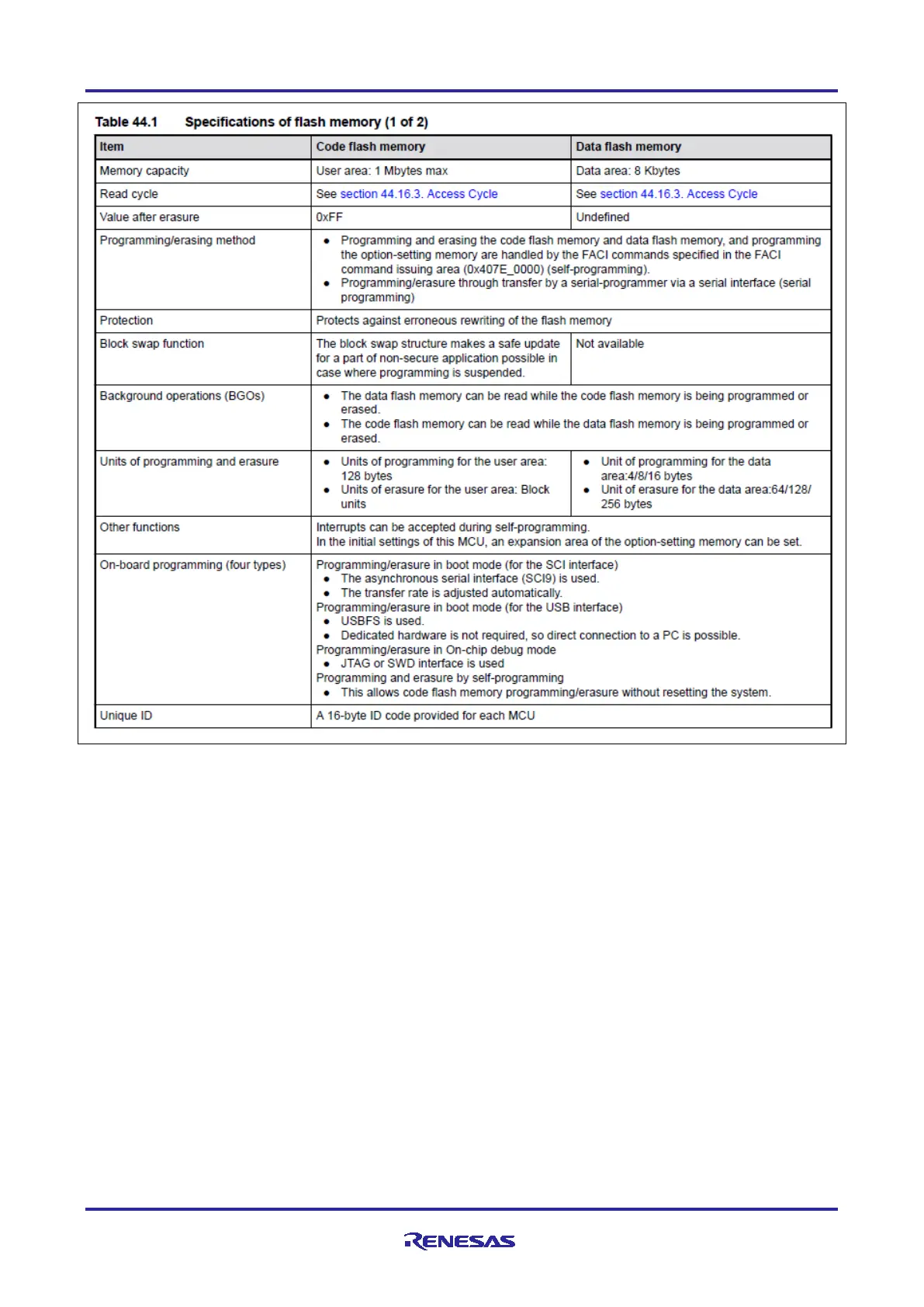

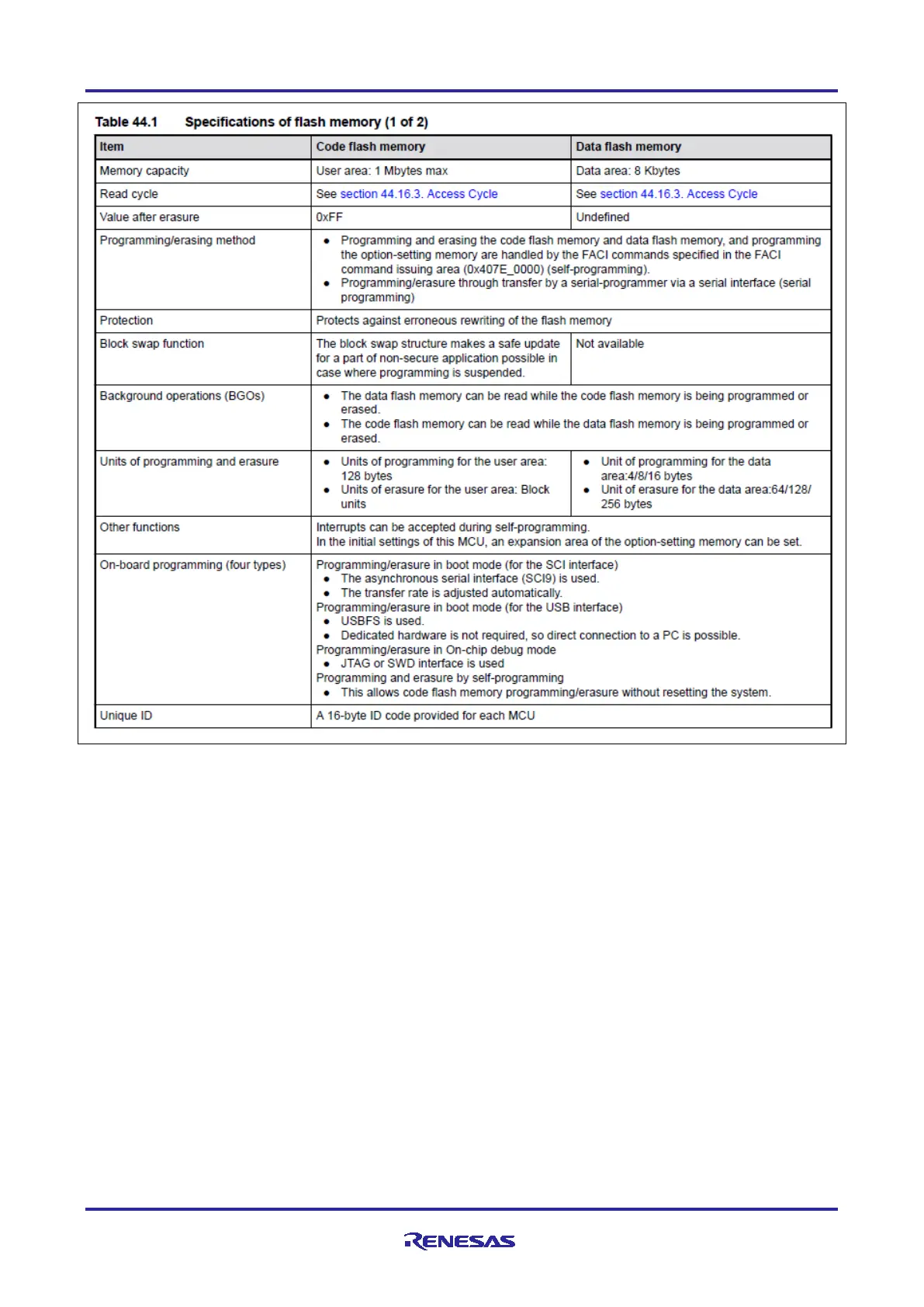

Figure 24. Specifications of Code Flash Memory and Data Flash Memory on RA4M3 MCU

Note: Erase state of code flash is FFh but erase state of data flash is undefined.

8.4.1 Background Operation

RA4 MCUs support background operations for code flash and data flash. This means that when a program

or erase is started, the user can keep executing and accessing memory from memory areas other than the

one being operated on. For example, the CPU can execute application code from code flash while the data

flash memory is being erased or programmed. Also, the CPU can execute application code from SRAM while

the code flash memory is being erased or programmed. The only exception to this rule is that the data flash

cannot be accessed during code flash programming or erasing.

8.4.2 ID Code Protection

RA4 MCUs with Arm Cortex-M4 core have a 128-bit memory in the option setting memory area that is used

as an ID code. If this ID code is left blank (0xFF’s) then no protection is enabled and access to the MCU is

allowed through boot mode or using the on-chip debugger. If the ID code is set then the user can control

access to these modes. The user can choose to always disallow connections or can choose to allow

connections when a matching ID code is input. Refer to the “OCD/Serial Programmer ID Setting Register

(OSIS)” and “ID Code Protection” and sections of RA4 MCU Hardware User’s Manual for more information.

The Renesas FSP configurator provides options to set up ID code protection for RA4 MCUs with the Arm

Cortex-M4 core.

Loading...

Loading...