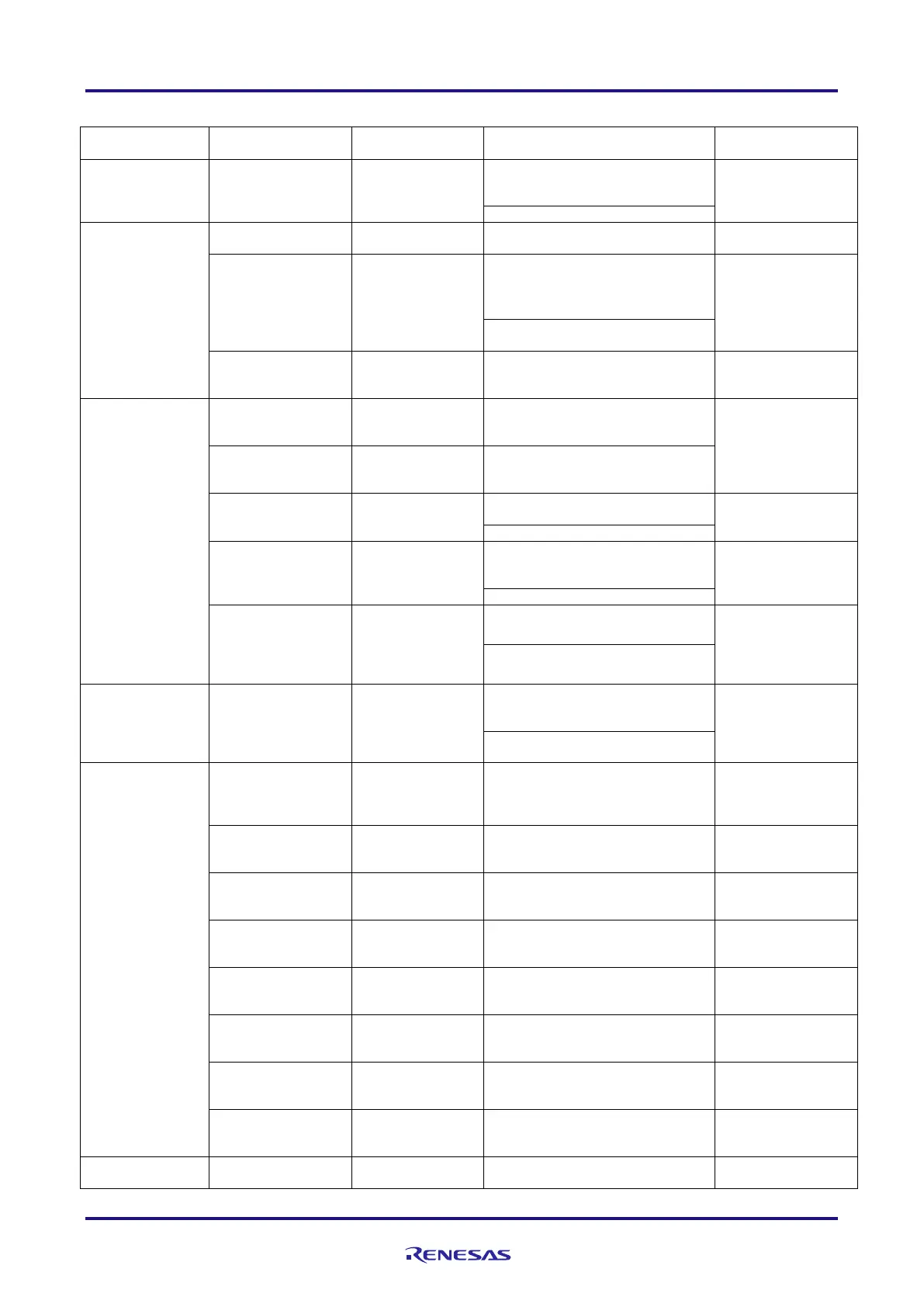

RH850 Series CAN Transmit Procedure (CAN FD Mode)

R01AN6029EJ0100 Rev.1.0 Page

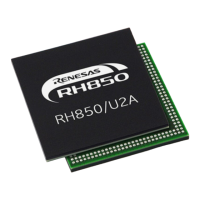

Configuration

(Enable) Unit *

1

Global receive

FIFO interrupt

Receive FIFOx

interrupt request

RFIE bit of the

RFCCx register

When the condition set by the

RFIGCV[2:0] bit of the RFCCx

register is met*

2

RFIF flag in the

RFSTSx register = ''0''

Every time one message is received

DEF flag in the

GERFL register

When the DLC check detects an error

DEF flag in the

GERFL register = "0"

MES bit of the

GERFL register

When a message lost in the

transmit/receive FIFO buffer is

detected

・ CFMLT flag in the

CFSTSk register of all

channels = ''0''. '

・ RFMLT flag in the

CRFSRx register of

all channels = ''0''

When a message lost in the receive

FIFO buffer is detected

Transmit history

buffer overflow

THLES flag in the

GERFL register

When the transmission history buffer

is full and you try to store more new

transmission history data

THLMLT flag in the

THLSTSm register of

all channels = ''0''

CANm transmist

complete interrupt

request

TMIIEp bit of the

TMIECy register

When the buffer becomes empty due

to the completion of message

transmission

TMTRF[1:0] flag in

the TMSTSp register

= ''B'00''.

CANm transmit abort

interrupt request

TAIE bit of the

CmCTR register

When the buffer becomes empty due

to the completion of sending a

message abort

CANm transmit queue

interrupt request

TQIE bit of the

TXQCCm register

When the send queue becomes empty

due to the completion of transmission

TQIF bit of the

TXQSTSm register =

"0"

Every time one message is sent

CANm

transmit /receive FIFO

transmission complete

interrupt request

CFTXIE bit of the

CFCCk register

When the buffer becomes empty due

to the completion of message

transmission

CFTXIF flag in the

CFSTSk register = ''0''

Every time one message is sent

CANm transmist

history interrupt

request

THIE bit of the

THLCCm register

When 12 data are stored in the

transmission history buffer

THIF flag in the

THLSTSm register =

''0''

Every time the transmission history

data is stored

CANm

transmit/receive

FIFO reception

completion

interrupt

Channel m transmit/

receive FIFO

reception complete

interrupt request

CFRXIE bit of the

CFCCk register

When the condition set by the

TRFRIT bit of the CFCCk register is

met*

3

CFRXIF flag in the

CFSTSk register = ''0''

Every time one message is received

BEIE bit of the

CmCTR register

When any one of the ADERR,

B0ERR, B1ERR, CERR, AERR,

FERR, and SERR flags of the

CmERFL register becomes "1".*

4

BEF flag in the

CmERFL register =

''0''

EWIE bit of the

CmCTR register

When the value of the REC [7: 0] or

TEC [7: 0] bit of the CmERFL

register exceeds 95

EWF flag in the

CmERFL register =

''0''

EPIE bit of the

CmCTR register

In case of the error passive state (REC

[7: 0] or TEC [7: 0] bits> 127).

EPF flag in the

CmERFL register =

''0''

BOEIE bit of the

CmCTR register

When the bus is off (TEC [7: 0] bits>

255)

BOEF flag in the

CmERFL register =

''0''

BORIE bit of the

CmCTR register

When 11-bit consecutive recessive

is detected 128 times and the bus is

restored from the off state.*

5

BORF flag in the

CmERFL register =

''0''

Overload frame

transmission

OLEE bit of the

CmCTR register

When the transmission condition of

the overloaded frame is detected when

receiving or transmitting

OVLF flag in the

CmERFL register =

'''0'''

BLIE bit of the

CmCTR register

When a 32-bit consecutive

dominant is detected on the CAN bus

in channel communication mode

BLF flag in the

CmERFL register =

''0''

ALIE bit of the

CmCTR register

When arbitration lost is detected

ALF flag in the

CmERFL register =

''0''

CAN bus falling edge

detection

When a falling edge is detected at the

CRXmD pin

Loading...

Loading...