Protocol Analysis

R&S

®

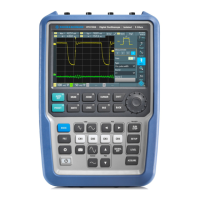

Scope Rider RTH

181User Manual 1326.1578.02 ─ 12

●

Addressing scheme: each slave device is addressable by a unique address. Multi-

ple slave devices can be linked together and can be addressed by the same mas-

ter.

●

Read/write bit: specifies if the master reads (=1) or writes (=0) the data.

●

Acknowledge: takes place after every byte. The receiver of the address or data

sends the acknowledge bit to the transmitter.

The R&S RTH supports all operating speed modes: high-speed, fast mode plus, fast

mode, and standard mode.

Data transfer

The format of a simple I²C message (frame) with 7-bit addressing consists of the fol-

lowing parts:

●

Start condition: a falling slope on SDA while SCL is high

●

7-bit address of the slave device that either is written to or read from

●

R/W bit: specifies if the data is written to or read from the slave

●

ACKnowledge bits: is issued by the receiver of the previous byte if the transfer was

successful

Exception: At read access, the master terminates the data transmission with a

NACK bit after the last byte.

●

Data: several data bytes with an ACK bit after every byte

●

Stop condition: a rising slope on SDA while SCL is high

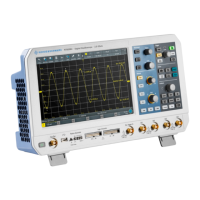

Figure 9-7: I2C writes access with 7-bit address

Address types: 7-bit and 10-bit

Slave addresses can be 7 bits or 10 bits long. A 7-bit address requires 1 byte, 7 bits for

the address followed by the R/W bit.

A 10-bit address for write access requires 2 bytes: the first byte starts with the reserved

sequence 11110, followed by the two MSB of the address and the write bit. The second

byte contains the remaining 8 LSB of the address. The slave acknowledges each

address byte.

I2C (Option R&S

RTH-K1)

Loading...

Loading...