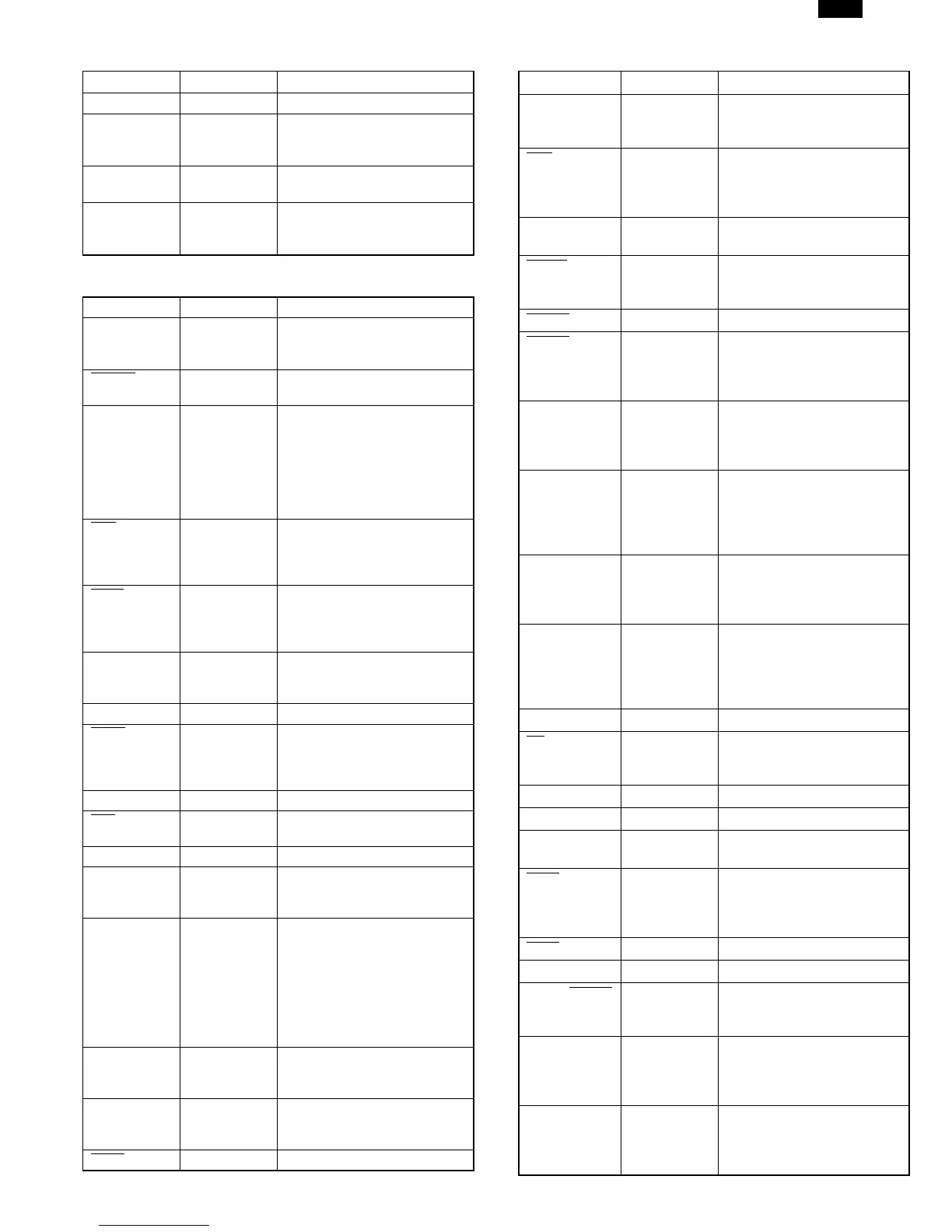

NSFX200 (IC503) supplies

Signal Pin Numbers Descrlption

GNDA1 ∼ 2 77 82 Analog ground.

GNDD1 ∼ 9 11 25 38

51 75 90

102 116 131

Digital ground.

VCCA1 ∼ 2 76 83 Analog Power — 5V supply

for analog circuits.

VCCD1 ∼ 9 5 17 32

50 66 84

96 109 125

Digital Power — 5V supply

for digital circuits.

Input Signals

Signal Pin Numbers Description

CTTL 33 CPU Clock — CPU clock that

is used for clocking the

NS32FX200.

DMRQ3 58 DMA Request — Input for

DMA channel 3 request.

FOSCI 36 High-Speed Oscillator —

(49.1520 MHz) Asynchronous.

When an external oscillator is

used, FOSCO should be left

unconnected or loaded with

no more than 5 pF of stray

capacitance.

HBE 117 High Byte Enable — Status

signal used to enable data

transfers on the most

significant byte of the data bus.

HLDA 114 Hold Acknowledge — Issued

by the CPU to indicate it has

released the bus in response

to a HOLD request.

INT0 ∼ 3 40 41 42

43

Interrupt In — Asynchronous.

External maskable prioritized

interrupt requests.

MWSI 57 General purpose input pin.

PFAIL 64 Power Fall Indication — An

asynchronous signal which

forces the NS32FX 200 into

freeze mode.

PTMP 81 Not used.

RST 61 Reset In — Asynhronous

reset input from the CPU.

SBG 80 Not used.

SDIN 19 Sigma-Delta Data In —

Asynchronous input from the

SDC analog receiver.

SOSCI 62 Low-Speed Oscillator —

(3.2768 kHz or 455 kHz)

Asynchronous. When an

external oscillator is used,

SOSCO should be left

unconnected or loaded with

no more than 5 pF of stray

capacitance.

SVI 78 Scanner Video In — Analog

current from the scanner

sample and hold circuit.

URXD 56 UART Recelve —

Asynchronous input or general

purpose input pin.

UTEN 55 General purpose input pin.

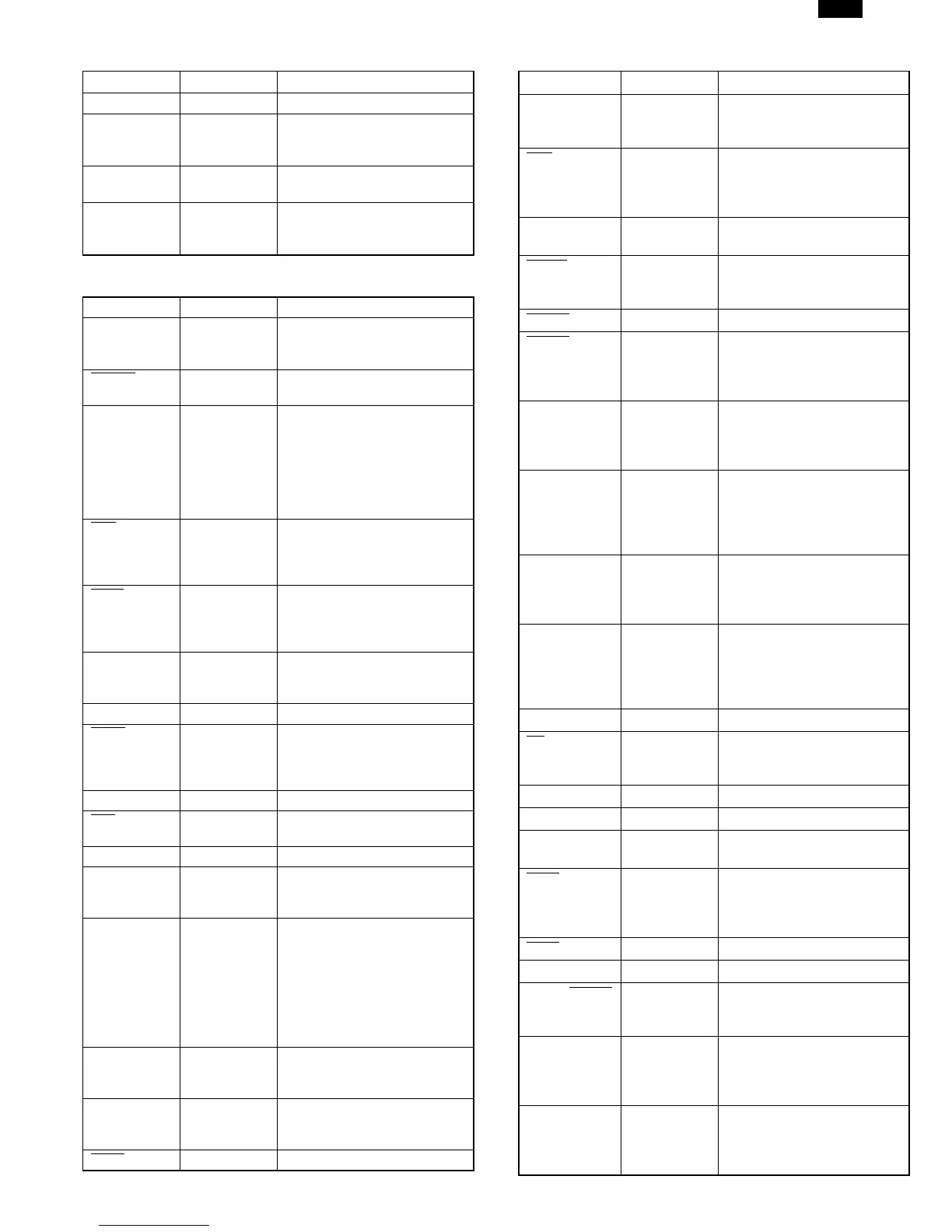

Output Signals

Signal Pin Numbers Description

BUZCLK 59 Buzzer Clock —

Programmable frequency

clock for the buzzer.

CAS 104 DRAM Column Address

Strobe — Column address

strobe for DRAM banks

refresh.

CCLK 39 CPU Double Clock — Feeds

CPU’S OSCIN. Asynchronous.

CWAIT 103 Continuous Walt — Low

extends the memory cycle of

the CPU.

DMAK1 28 General purpose output pin.

DMAK3 26 DMA Acknowledge —

Output for DMA channel 3

acknowledge or general

purpose output pin.

FOSCO 37 High-Speed Oscillator Out —

Asynchronous.This line is

used as the return path for

the crystal (if used).

HOLD 115 Hold Request — When low,

HOLD requests the bus from

the CPU to perform DMA

operations or to insert idle

bus cycles.

INTR 44 Interrupt Request — Low

indicates that an interrupt

request is being output to the

CPU.

MA1 ∼ 15 101 100 99

98 97 95

94 93 92

91 89 88

87 86 85

Memory Address Bus —

Multiplexed DRAM address.

MWSK 24 General purpose output pin.

OE 111 Output Enable — Used by

the addressed device to gate

the data onto the data bus.

PDO 16 Not used.

PEXT 65 Not used.

PMPH0 ∼ 3 74 73 72

71

Output port.

RAS0 106 DRAM Row Address

Strobes — Row address

strobe for DRAM banks 0

and 1.

RAS1 105 RAS1 is not used.

SCLK1 22 General purpose output pin.

SCLK2/DAMK0 29 Scanner Clock 2 — Output,

DMA Acknowledge-output for

DMA channel 0 acknowledge.

SCVO 79 Scanner Compensated

Video Out — Analog current

for use by ABC or optional

video enhanement circuit.

SDFDBK 18 Sigma-Delta Feedback —

Feedback input to the SDC

analog receiver.

Asynchronous output signal.

AR-F152

12 – 14

Loading...

Loading...