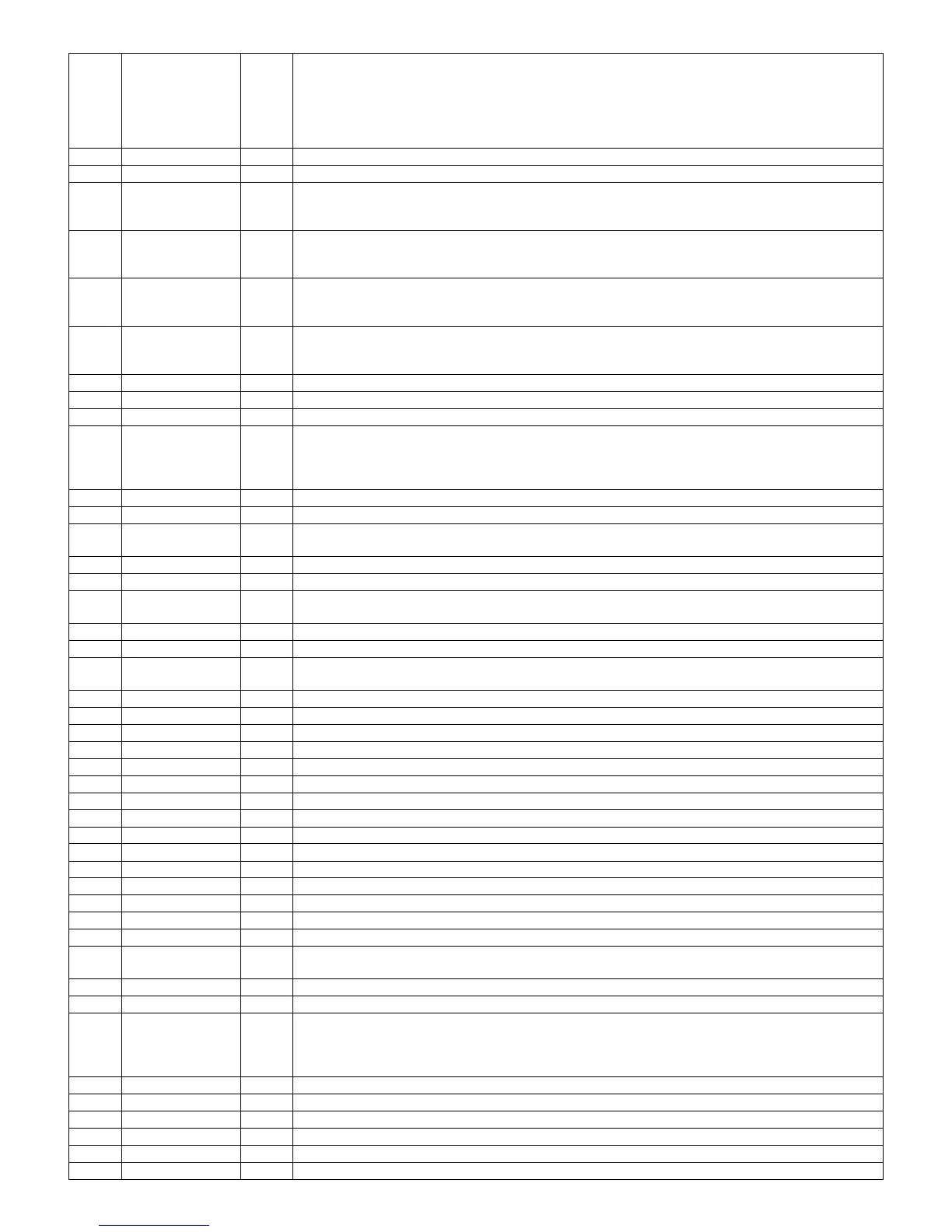

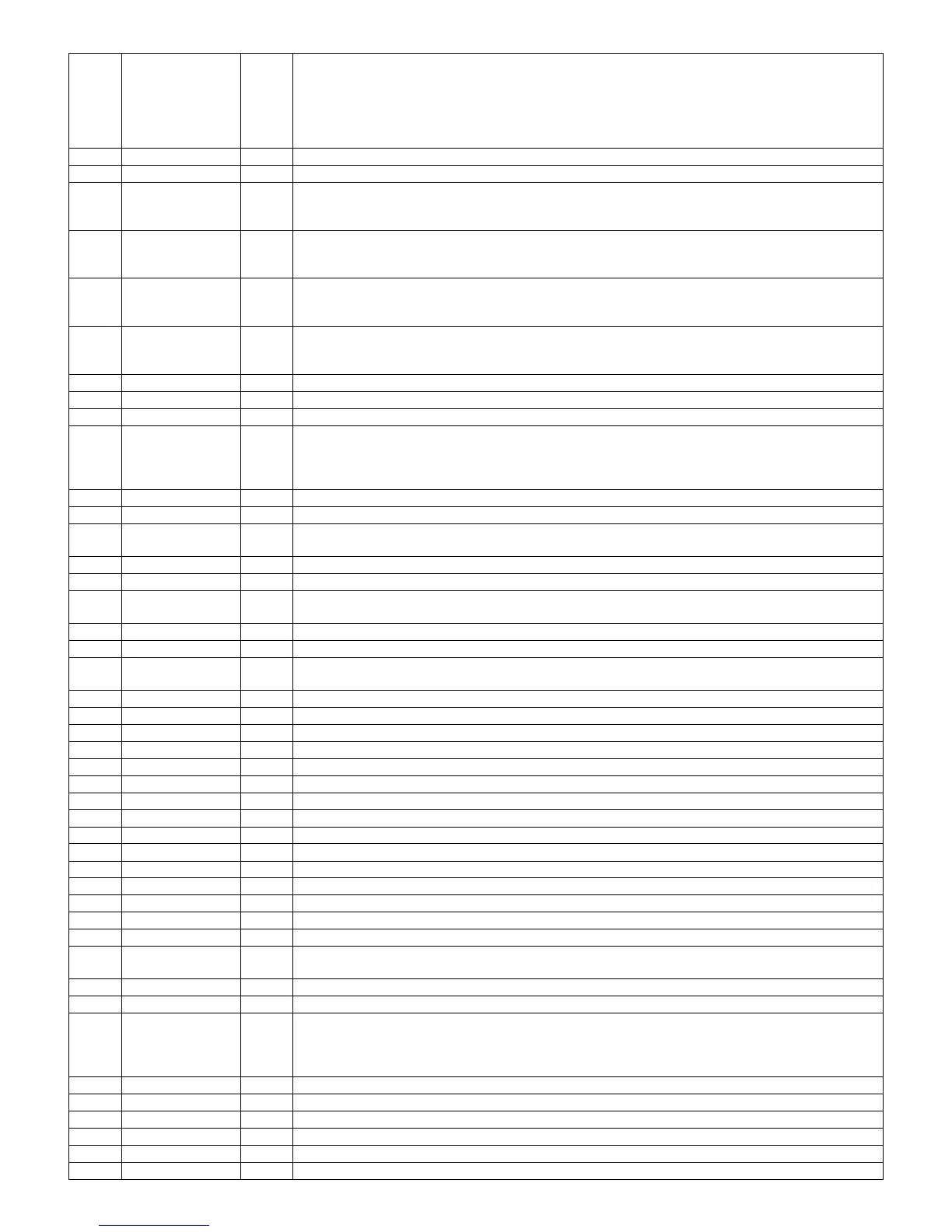

LC-37XD1E/RU

5 – 12

78 UVOUT4/

INTR

O Tristate ( ENITUE=0)

Digital (chrominance/blue) output (ENITUE=1 and SELRB=0)

Digital (chrominance/red) output (ENITUE=1 and SELRB=1)

Interrupt signal output from µC (CPUIRQ=5)

Static 0 (CPUIRQ=6)

Static 1 (CPUIRQ=7)

79 VDDP6 S Supply digital pad (3.3 V)

80 VSSP6 S Supply digital pad (0 V)

81 UVOUT3 O

Tristate (ENITUE=0)

Digital (chrominance/blue) output (ENITUE=1 and SELRB=0)

Digital (chrominance/red) output (ENITUE=1 and SELRB=1)

82 UVOUT2 O

Tristate (ENITUE=0)

Digital (chrominance/blue) output (ENITUE=1 and SELRB=0)

Digital (chrominance/red) output (ENITUE=1 and SELRB=1)

83 UVOUT1 O

Tristate (ENITUE=0)

Digital (chrominance/blue) output (ENITUE=1 and SELRB=0)

Digital (chrominance/red) output (ENITUE=1 and SELRB=1)

84 UVOUT0 O

Tristate (ENITUE=0)

Digital (chrominance/blue) output (ENITUE=1 and SELRB=0)

Digital (chrominance/red) output (ENITUE=1 and SELRB=1)

85 VDDD4 S Supply digital core (1.8 V)

86 VSSD4 S Supply digital core (0 V)

87 VDDA0 S Supply analog DAC SVM (3.3 V)

88 ASVMOUT O

Middle level (STANDBY=1)

Analog SVM output (ACTFBL=0 and STANDBY=1)

Analog SVM output (control by SVMOFF possible)

(ACTFBL=1 and STANDBY=0)

89 VSSA0 S Supply analog DAC SVM (0 V)

90 VDDA1 S Supply analog DAC B/U (3.3 V)

91 AUOUT O

Middle level (STANDBY=0)

Chrominance output (STANBY=1)

92 VSSA1 S Supply analog DAC B/U (0 V)

93 VDDA2 S Supply analog DAC G/Y (3.3 V)

94 AYOUT O

Middle level (STANDBY=0)

Luminance output (STANDBY=1)

95 VSSA2 S Supply analog DAC G/Y (0 V)

96 VDDA3 S Supply analog DAC R/V (3.3 V)

97 AVOUT O

Middle level (STANDBY=0)

Chrominance output (STANDBY=1)

98 VSSA3 S Supply analog DAC R/V (0 V)

99 VSSA4 S Supply analog band gap (0 V)

100 VDDA4 S Supply analog band gap (3.3 V)

101 VSSD5 S Supply digital core (0 V)

102 VDDD5 S Supply digital core (1.8 V)

103 NC - No Connection

104 NC - No Connection

105 SCL I/O I2C bus clock

106 SDA I/O I2C bus data

107 NC - No Connection

108 NC - No Connection

109 VSSP7 S Supply digital pad (0 V)

110 VDDP7 S Supply digital pad (3.3 V)

111 TMS I Test mode select (3.3 V)

112 NC - No Connection

113

TDO/

SVMOFF

O/I

Test data out (ACTSVMOFF=1)

SVM input signal (ACTSVMOFF=0)

114 TDI I Test data in (0V)

115 TCLK I Test clock (3.3 V)

116 INTR O

Interrupt signal

Static 0 (CPUIRQ2=00)

Static 1 (CPUIRQ2=01)

Interrupt signal output from µC (CPUIRQ2= 1x)

117 656I02 I Digital (luminance) input [LSB]

118 656I12 I Digital (luminance) input

119 656I22 I Digital (luminance) input

120 656I32 I Digital (luminance) input

121 656I42 I Digital (luminance) input

122 656I52 I Digital (luminance) input

Loading...

Loading...