LC-37XD1E/RU

5 – 15

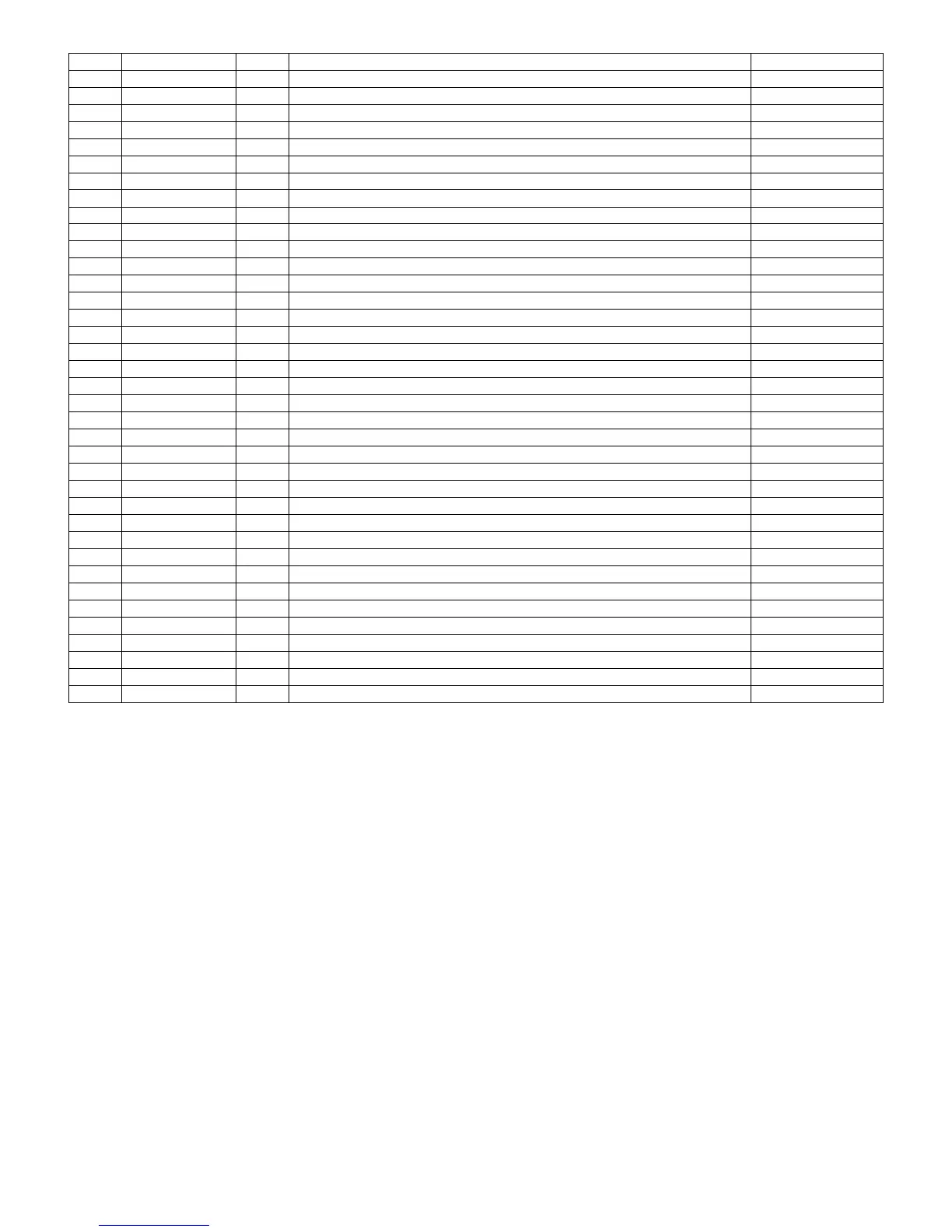

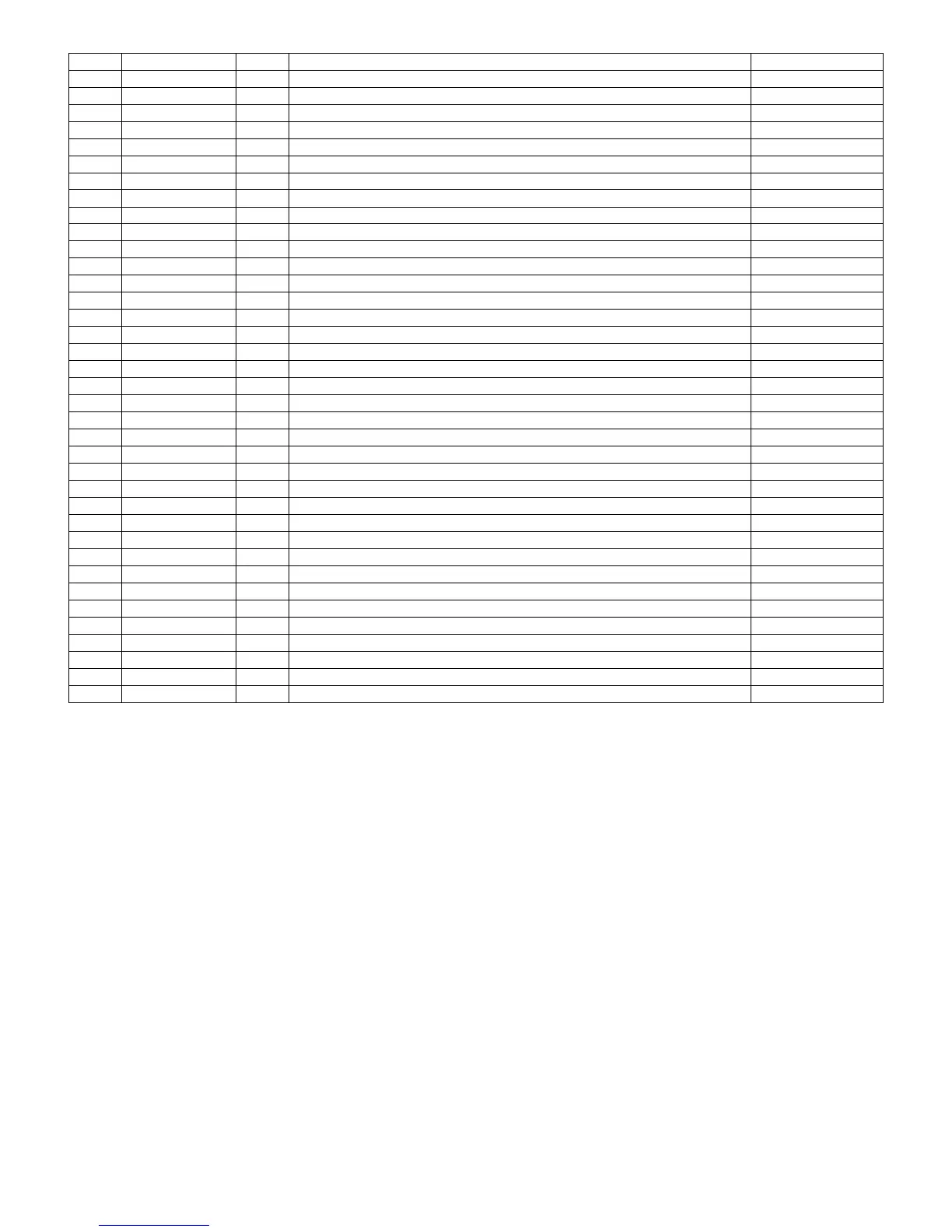

63 VCCINT 3.3V - Power supply 3.3V 3.3V

64 SCK I from VGC SCK

65 GND - Ground GND

66 SEN I from VGC FPGA_SDE

67 SDAI I from VGC FPGA_SDA

68 I/O - GND* NC

69 SDAO O Write mode RESET output FPGA_SDAO

70 I/O - GND* NC

71 I/O - GND* NC

72 I/O - GND* NC

73 I/O - GND* NC

74 I/O - GND* NC

75 OFL2EN I OFL2_EN external setting terminal GND

76 I/O - GND* NC

77 I/O O VGC write Open drain (Write mode at "H") BOOT

78 I/O - GND* NC

79 GND - Ground GND

80 VCCIO2 3.3V - Power supply 3.3V 3.3V

81 I/O I VSYNC_OSC VSYNC

82 I/O I HSYNC_OSC HSYNC

83 I/O - GND* NC

84 I/O - GND* NC

85 EXP[0] O DTI2CSEL DTI2CSEL

86 EXP[1] O DTM_RESET DTM_RESET

87 EXP[2] O DTU_ON (Analog tuner at "L" D-tuner at "H") DTU_ON

88 EXP[3] O 232C on/off SW (RS232C action at "H": VGC write enabled) IREM_SW

89 EXP[4] O STB (LAMP ON) STB

90 EXP[5] O S2_MUTE S2MUTE

91 EXP[6] O ANT+5V ON ANT+5V ON

92 EXP[7] O S_MUTE S-MUTE

93 GND - Ground GND

94 VCCIO2 3.3V - Power supply 3.3V 3.3V

95 I/O - GND* NC

96 I/O - GND* NC

97 I/O - GND* NC

98 I/O - GND* TP1703

99 I/O - GND* NC

100 OFL-SET-IN I OFLWD[8] external setting terminal GND

GND*: Non-configured pins are fixed at GND.

Terminals' electrical characteristics are referred to in the EPM240T100C5N data sheet of Altera.

Note 1: Reset output monitor terminal with EXP31 in use.

Note 2: Composed of GCLR and OR.

Loading...

Loading...