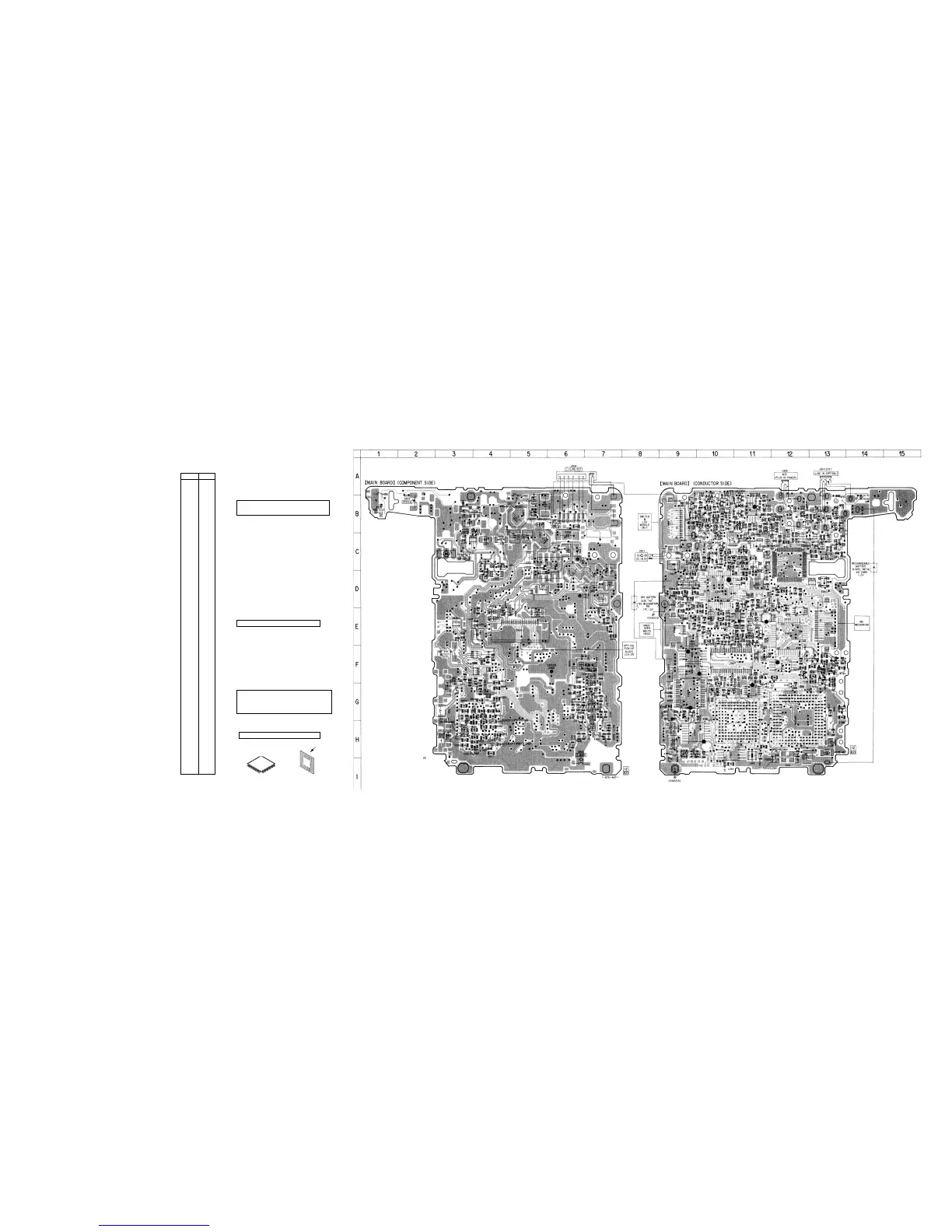

Lead layout of conventional IC CSP (chip size package)

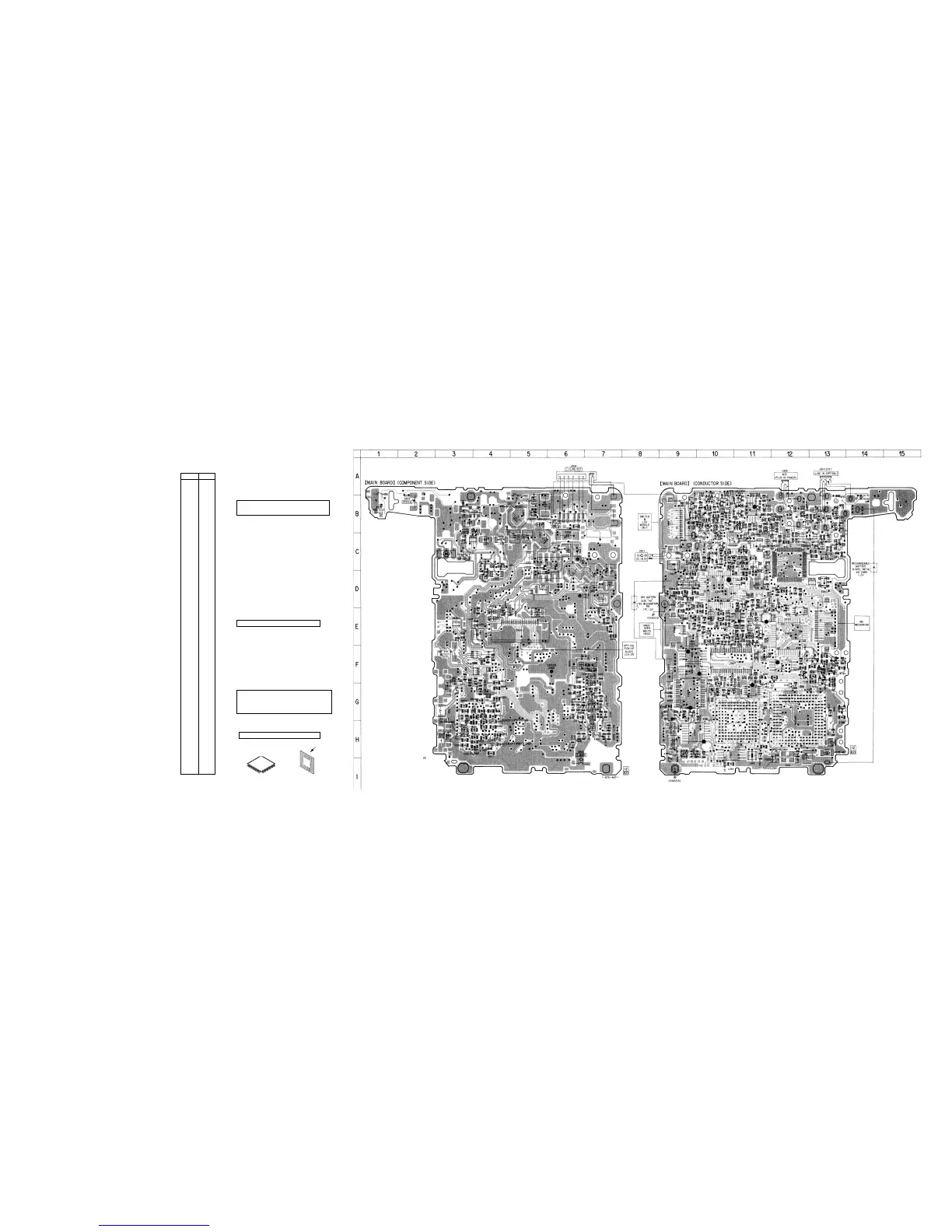

Note on Printed Wiring Board:

• X : parts extracted from the component side.

• Y : parts extracted from the conductor side.

• x : parts mounted on the conductor side.

•

z

: Through hole.

• b : Pattern from the side which enables seeing.

(The other layers' patterns are not indicated.)

Caution:

Pattern face side: Parts on the pattern face side seen from

(Conductor Side) the pattern face are indicated.

Parts face side: Parts on the parts face side seen from

(Component Side) the parts face are indicated.

Note on Schematic Diagram:

• All capacitors are in µF unless otherwise noted. pF: µµF

50 WV or less are not indicated except for electrolytics

and tantalums.

• All resistors are in Ω and

1

/

4

W or less unless otherwise

specified.

• % : indicates tolerance.

•

f

: internal component.

• C : panel designation.

• A : B+ Line.

• Power voltage is dc 3 V and fed with regulated dc power

supply from external power voltage jack.

• Voltages and waveforms are dc with respect to ground

under no-signal conditions.

no mark : PLAYBACK

( ) : RECORD

∗

: Impossible to measure

• Voltages are taken with a VOM (Input impedance 10 MΩ).

Voltage variations may be noted due to normal produc-

tion tolerances.

• Waveforms are taken with a oscilloscope.

Voltage variations may be noted due to normal produc-

tion tolerances.

• Circled numbers refer to waveforms.

• Signal path.

E : PLAYBACK (ANALOG OUT)

j : PLAYBACK (ANALOG IN)

l : RECORD (DEGITAL IN)

• Abbreviation

CND : Canadian model

FR : French model

HK : Hong Kong model

JEW : Tourist model

Note: The components identified by mark 0 or dotted line

with mark 0 are critical for safety.

Replace only with part number specified.

*

IC502 and IC801 are not replaceable

• The voltage and waveform of CSP (chip size package) can-

not be measured, because its lead layout is different form

that of conventional IC.

Ver 1.2 2000. 02

Loading...

Loading...