LE910Cx mPCIe Hardware Design Guide

1VV0301510 Rev. 13 Page 29 of 73 2021-07-07

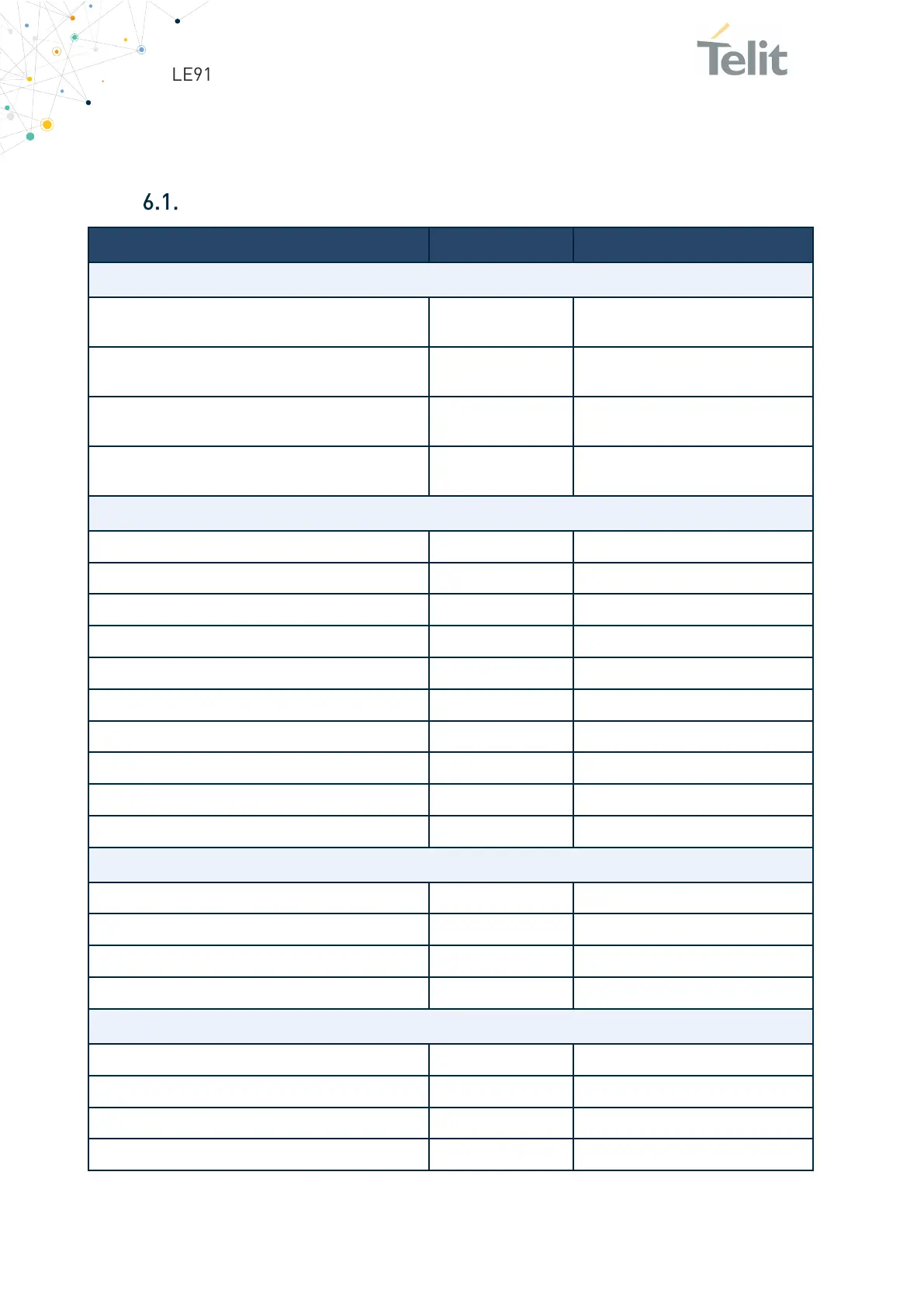

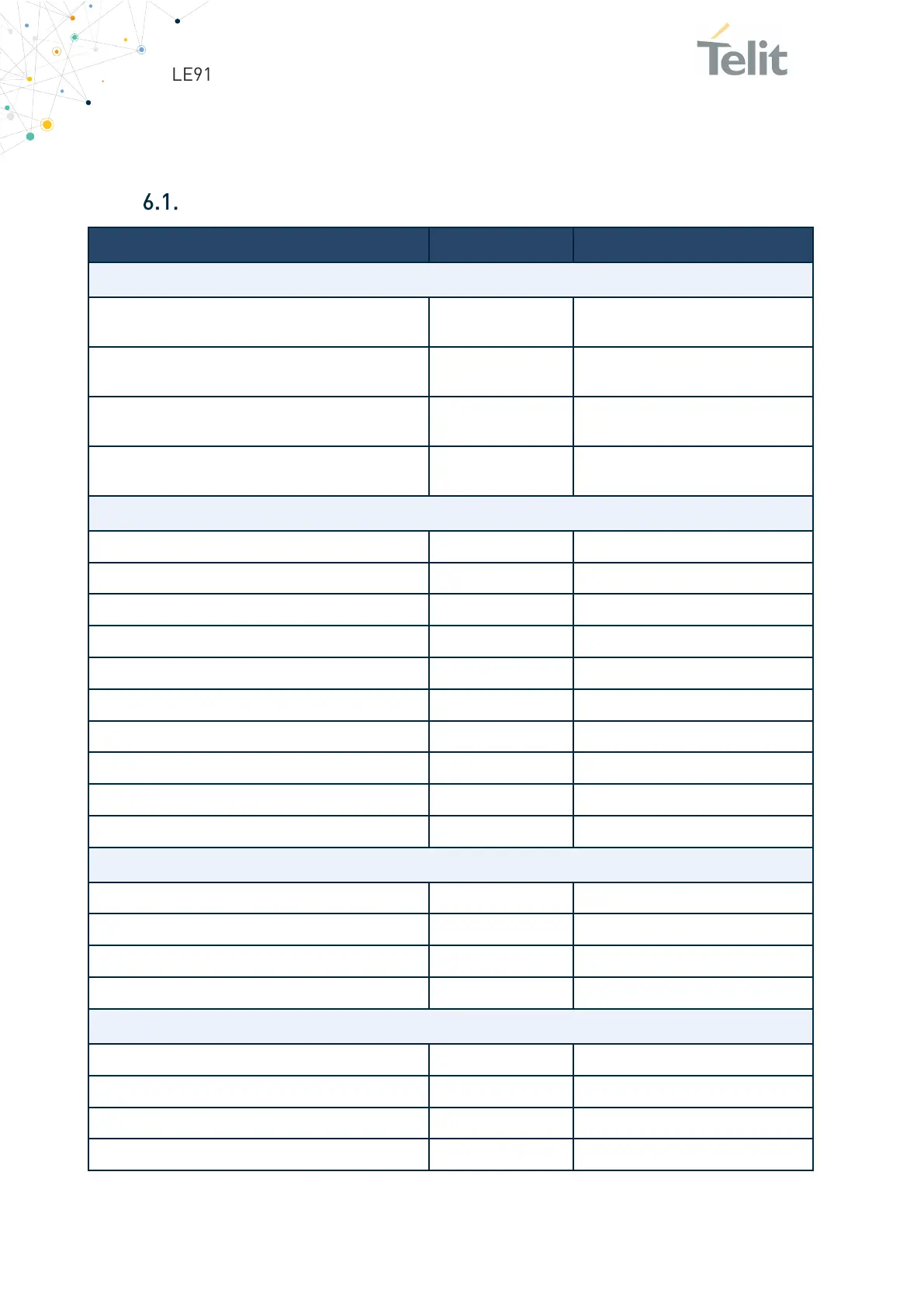

6. DIGITAL SECTION

Logic Levels

Input level on any digital pin (CMOS 1.8) with

respect to ground

-0.3V 2.16V

Input level on any digital pin (CMOS 1.8) with

respect to ground when VBATT is not supplied

-0.3V 0.3V

Input level on any digital pin (CMOS 3.3) with

respect to ground

-0.3V 3.6V

Input level on any digital pin (CMOS 3.3) with

respect to ground when VBATT is not supplied

-0.3V 0.3V

OPERATING RANGE – INTERFACE LEVELS 1.8 V CMOS:

Low-level input leakage current, no pull-up

High-level input leakage current, no pull-down

OPERATINGS RANGE – INTERFACE LEVELS 3.3 V CMOS:

OPERATING RANGE – SIM CARD PADS @ 2.95 V

Loading...

Loading...