Alto Hardware Manual

. Section

8:

Control RAM,

ROM,

and s Registers

57

4

RAM/ROM

o Means operate

on

the control

RAM.

1 Means operate

on

the control

ROM.

(This doesn't quite work the

way

you might

think. See section

8.8

for details.)

5

HALFSEL

- Ignored when writing

o Means read out the low-order 16-bits

of

the addressed word.

1 Means read out the high-order 16-bits

of

the addressed word.

6-15

Word address (0-1023).

Since

it

is

expected that reading the control

RAM

will

be

a relatively infrequent operation, a single

assertion

of

RDRAM

reads

out

only one half

of

a 32-bit control

RA.l\1

(or

ROM)

word onto the processor.

bus.

To

read out both halves, the control

RAM

address register must be loaded twice

and

RDRAM

invoked twice. Data resulting from

RDRAM

is

AND'ed

onto the processor bus during the microinstruction

following that in which the

RDRAM

was

asserted.

In contrast,

it

is expected that writing into the control

RAM

will occur frequently. Therefore a single

application

of

WRTRAM

writes both halves

of

a control

RAM

word

at

once. The M register contents (see

section

8.7)

after the microinstruction containing the

WRTRAM

will

be written into the high-order

half

of

the addressed control

RAM

word. The

ALU

output during the microinstruction following the

WRTRAM

will be written into the low-order half. This protocol mates well with doubleword main memory reads.

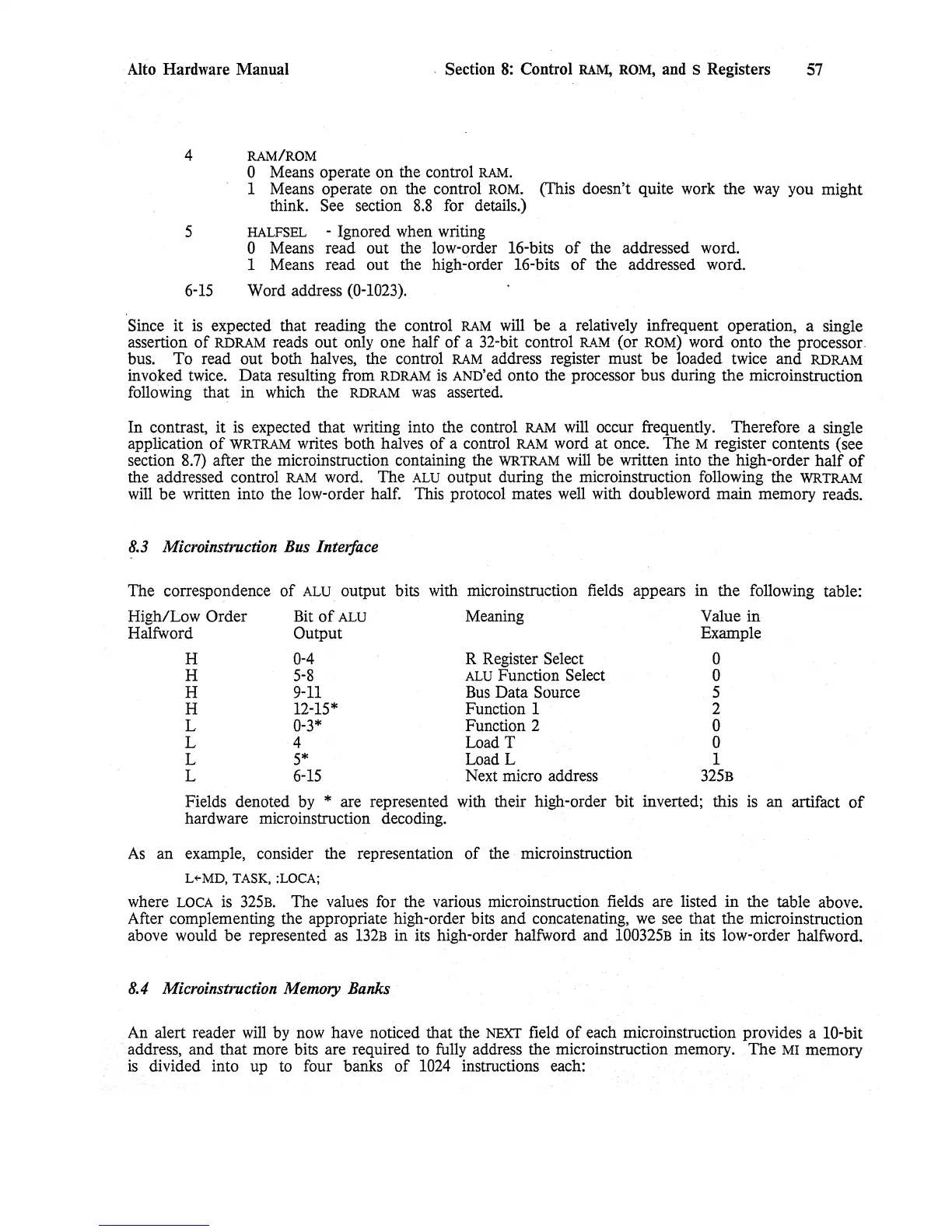

8.3

Microinstruction Bus Interface

The correspondence

of

ALU.

output bits with microinstruction fields appears in

the

following table:

High/Low

Order Bit

of

ALU

Meaning Value

in

Halfword Output Example

H

0-4

R Register Select 0

H

5-8

ALU

Function Select 0

H

9-11

Bus

Data Source 5

H 12-15* Function 1 2

L

0-

3 * Function 2 0

L 4

LoadT

0

L

5*

Load L 1

L

6-15

Next micro address

325B

Fields denoted by * are represented with their high-order

bit

inverted; this is an artifact

of

hardware microinstruction decoding.

As

an example, consider the representation

of

the· microinstruction

L+-MD,

TASK,

:LOCA;

where

LOCA

is

325B.

The values for the various microinstruction fields are listed

in

the table above.

After complementing the appropriate high-order bits and concatenating, we see that the microinstruction

above would

be

represented as

132B

in its high-order halfword and

100325B

in its low-order halfword.

8.4

Microinstruction Memory Banks

An alert reader will by now have noticed that the

NEXT

field

of

each microinstruction provides a lO-bit

address, and that more bits are required to fully address the microinstruction memory.

The

Ml

memory

is

divided into up to four banks

of

1024 instructions each:

Loading...

Loading...