Circuit examples

187

1SVC 440 795 M0100

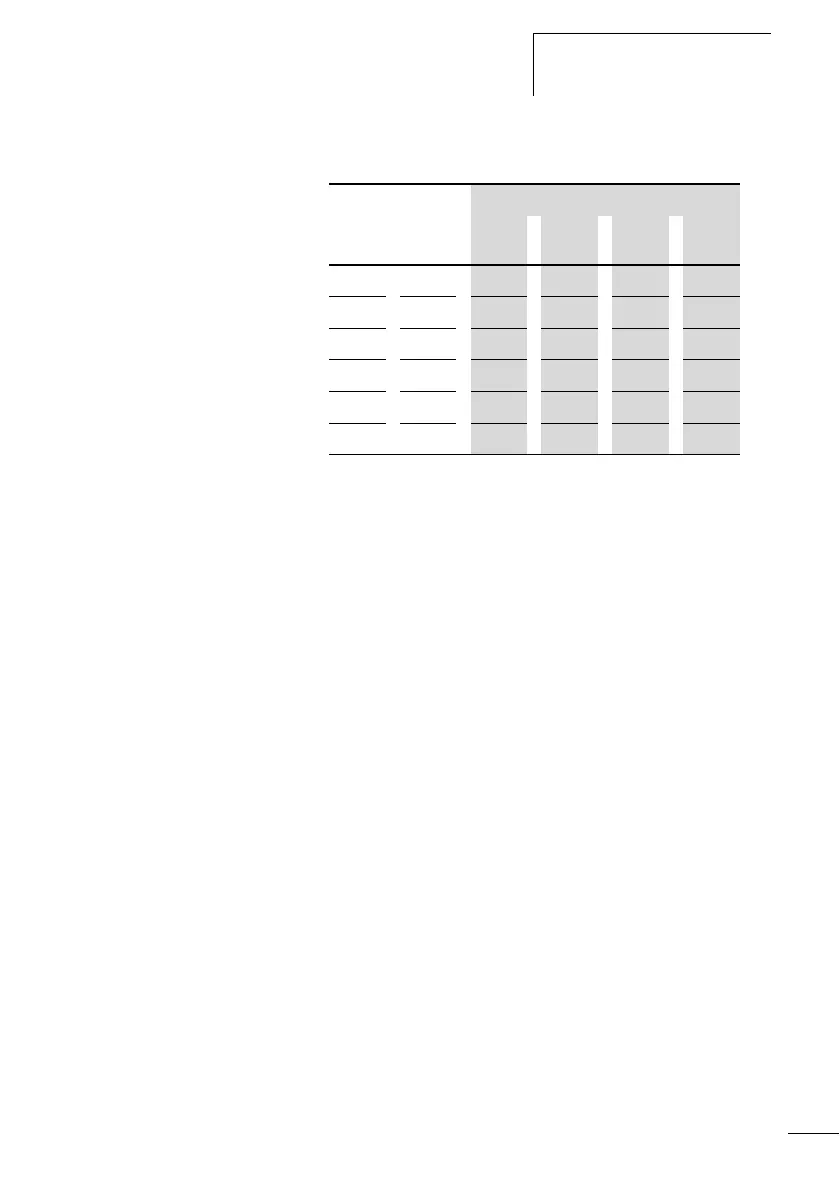

Table 26: Shift register

Assign the information “bad” to value 0. If the shift register

is cleared accidentally, no bad parts are used further.

• I1: Shift pulse (PULSE)

• I2: Information (good/bad) to be shifted (VALUE)

• I3: Clear content of the shift register (RESET)

• M1: 1st storage location

• M2: 2nd storage location

• M3: 3rd storage location

• M4: 4th storage location

• M7: Marker relay for cycle pulse

• M8: Cyclical pulse for shift pulse

Pulse Value Storage position

1 2 3 4

111 0 0 0

200 1 0 0

300 0 1 0

411 0 0 1

500 1 0 0

Reset = 1 0 0 0 0

Loading...

Loading...