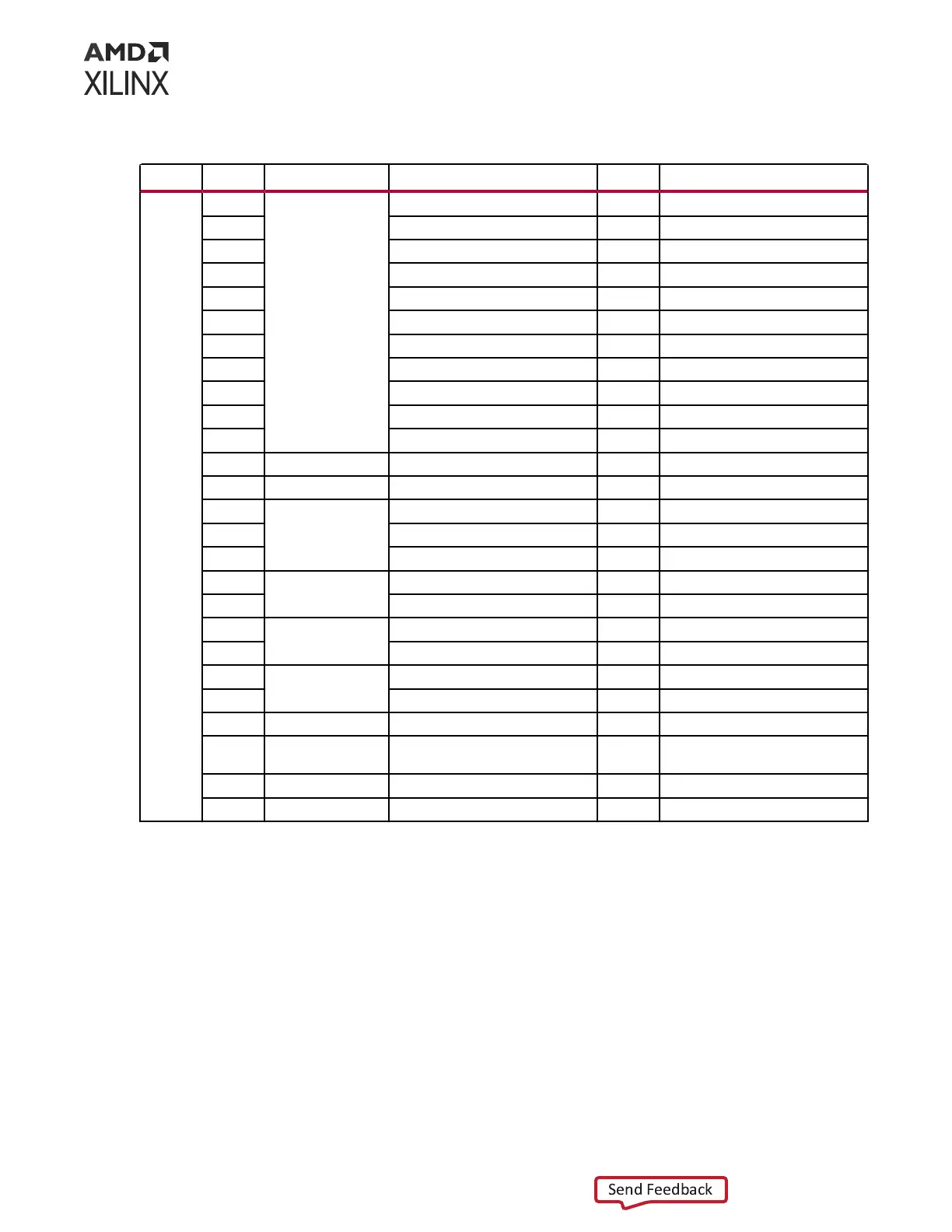

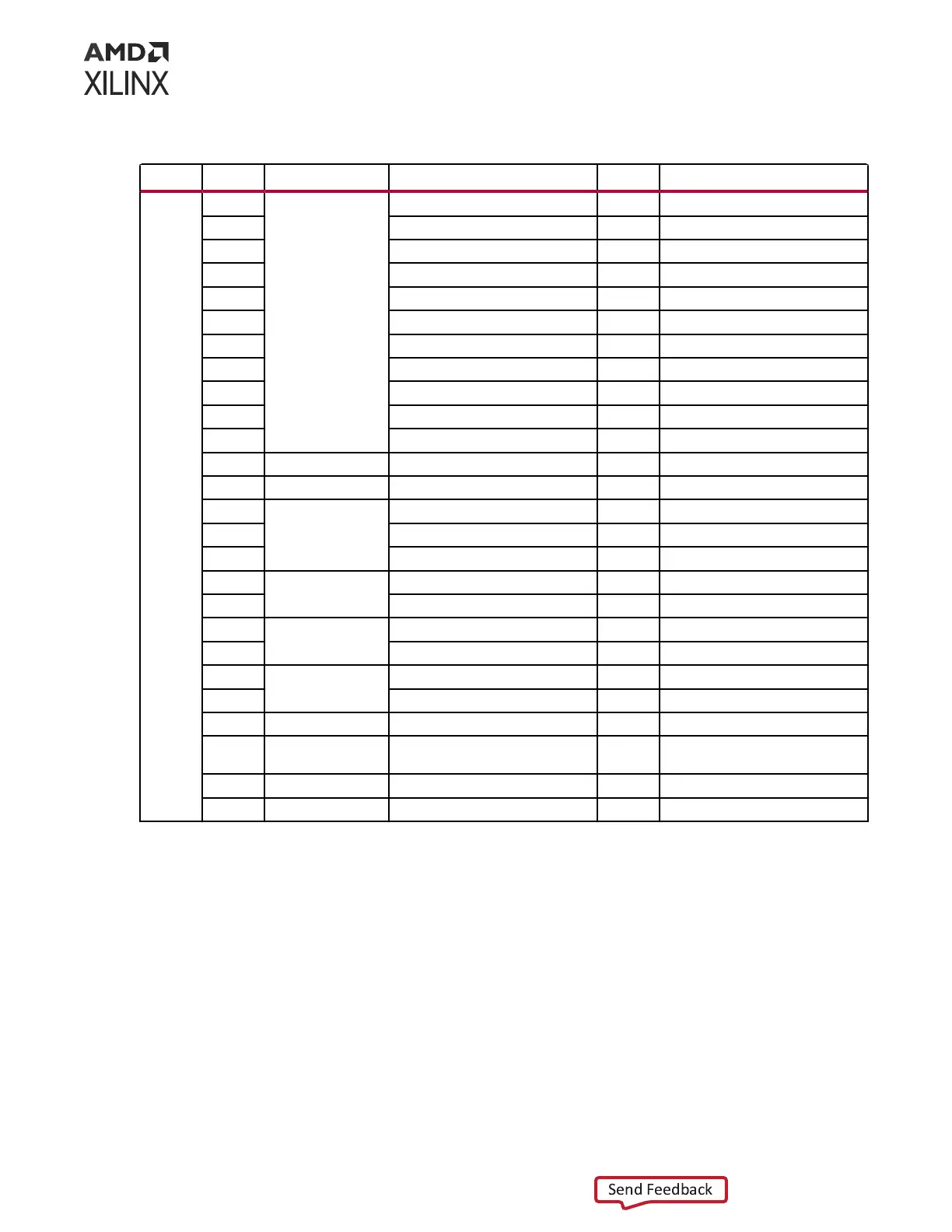

Table 7: MIO Peripheral Mapping (cont'd)

Bank MIO # Device Signal I/O Notes

501 26 SD PMC_MIO26_SD_CLK O SD CLK

27 PMC_MIO27_SD_DIR1 O SD CLK

28 PMC_MIO28_SD_DET I SD DETECT

29 PMC_MIO29_SD_CMD I/O SD CMD

30 PMC_MIO30_SD_DAT0 I/O SD DAT0

31 PMC_MIO31_SD_DAT1 I/O SD DAT1

32 PMC_MIO32_SD_DAT2 I/O SD DAT2

33 PMC_MIO33_SD_DAT3 I/O SD DAT3

34 PMC_MIO34_SD_SEL I/O SD SEL

35 PMC_MIO35_SD_DIR_CMD O SD DIR_CMD

36 PMC_MIO36_SD_DIR0 O SD DIR0

37 SYSCTLR PMC_MIO37_501_ZU4_TRIGGER I/O PMC_MIO37_501_ZU4_TRIGGER

38

39 SYSMON I2C PMC_MIO39_SYSMON_I2C_SCL I/O SYSMON I2C SCL

40 PMC_MIO40_SYSMON_I2C_SDA I/O SYSMON I2C SDA

41 PMC_MIO41_SYSMON_I2C_ALERT I/O SYSMON_I2C_ALERT

42 UART PMC_MIO42_501_RX_IN I UART RX

43 PMC_MIO43_501_TX_OUT O UART TX

44 I2C1 PMC_MIO44_501_LP_I2C1_SCL I/O I2C1 SCL

45 PMC_MIO45_501_LP_I2C1_SDA I/O I2C1 SDA

46 I2C0 PMC_MIO46_501_I2C0_SCL I/O I2C0 SCL

47 PMC_MIO47_501_I2C0_SDA I/O I2C0 SDA

48 PMC_MIO48_501 O GEM0 RESET

49 Regulator Enable

GPIO

VCC_PSLP_EN_LS O PSLP Power Enable

50

51 SD PMC_MIO51_SD_BUSPWR O SD BUSPWR

Chapter 3: Board Component Descriptions

UG1582 (v1.0) February 21, 2023 www.xilinx.com

VPK180 Board User Guide 31

Loading...

Loading...