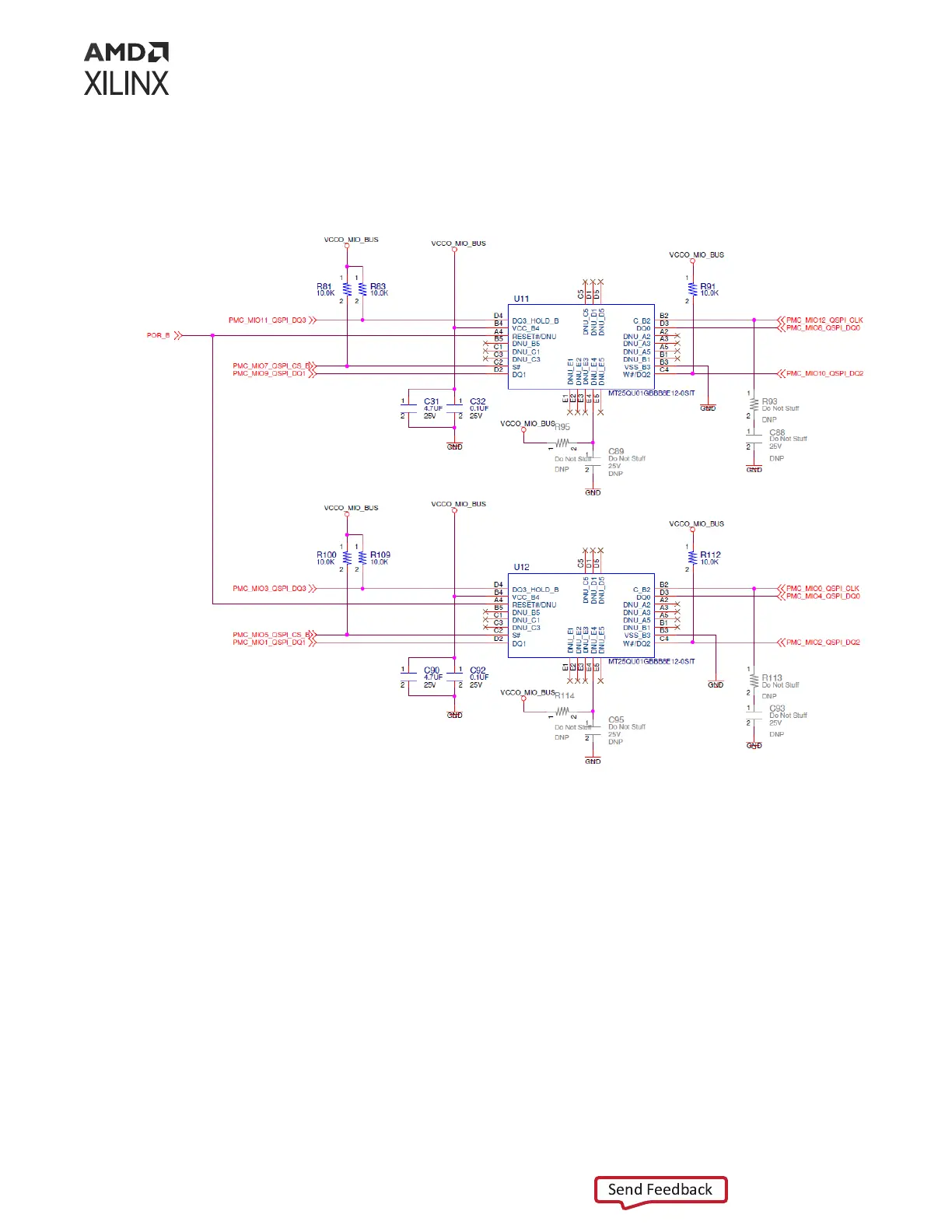

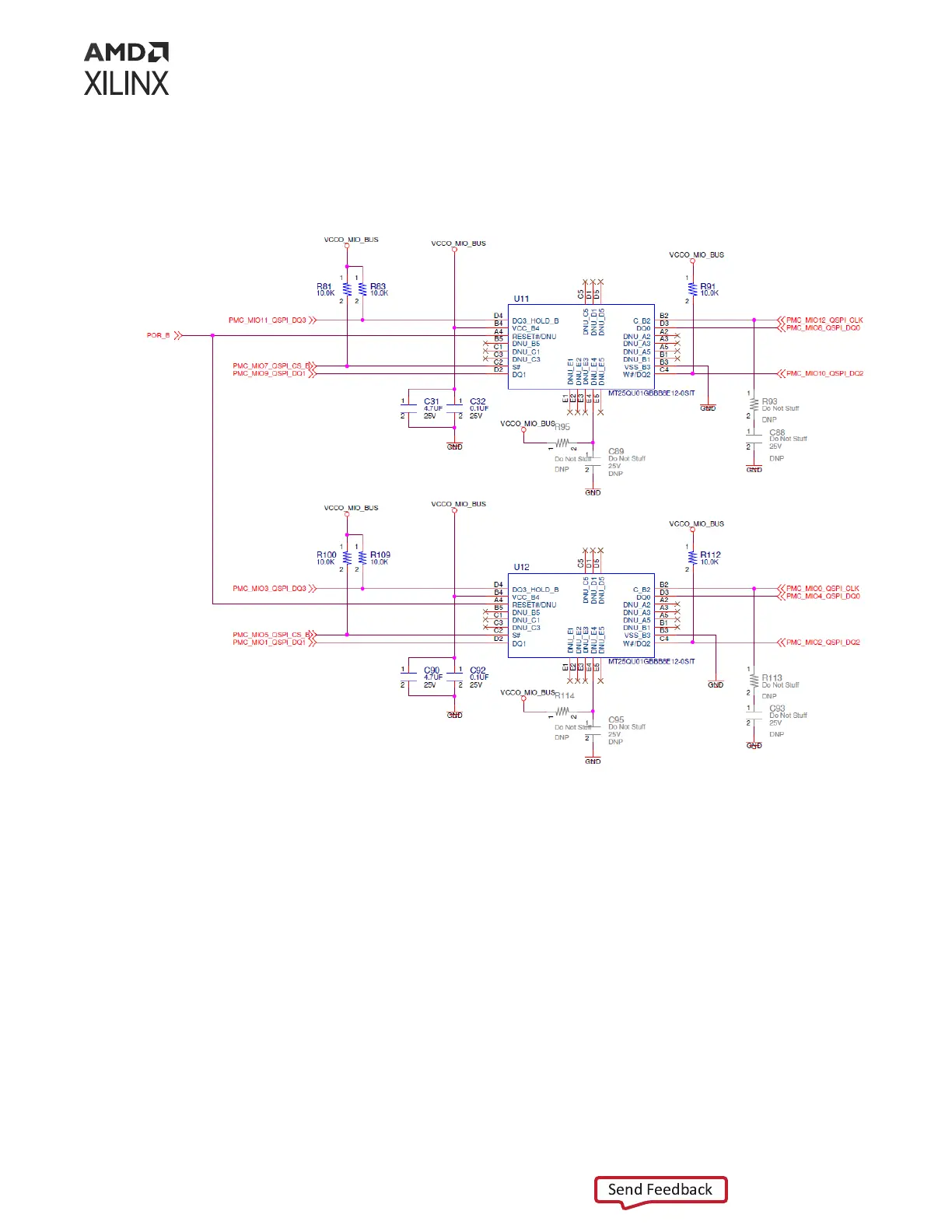

See schemac pages 12 and 33.

Figure 8: Dual Parallel QSPI Circuit

X26295-021422

PMC MIO[13:25] Bank 500: USB 2.0 ULPI PHY

The VPK180 evaluaon board uses a Standard Microsystems Corporaon USB3320 USB 2.0

ULPI transceiver (U99) to support a USB 2.0 type-A connector (J308). The USB3320 is a high-

speed USB 2.0 PHY supporng the UTMI+ low pin interface (ULPI) interface standard. The ULPI

standard denes the interface between the USB controller IP and the PHY device, which drives

the physical USB signaling. Using the ULPI standard reduces the interface pin count between the

USB controller IP and the PHY device.

The USB3320 is clocked by a 24 MHz crystal (X8). See the Standard Microsystems Corporaon

(SMSC) USB3320 data sheet for clocking mode details. The interface to the USB3320 PHY is

implemented through the IP in the XCVP1802 ACAP PS.

Chapter 3: Board Component Descriptions

UG1582 (v1.0) February 21, 2023 www.xilinx.com

VPK180 Board User Guide 33

Loading...

Loading...