AN-877 Application Note

Rev. B | Page 14 of 20

Output Mode (0x014)

Bit 7 to Bit 6—Logi c Type

Bit 7 to Bit 6 control the output logic type. The setting of these

bits corresponds to the type of output logic selected. These are

only specified as Level Option 0 through Level Option 3, and

are defined in the device data sheet. Low voltage differential

signaling (LVDS) type outputs, if used, can also work with

0x015 to determine output termination and driver current.

Complementary metal-oxide semiconductor (CMOS) type

outputs may also work with 0x015 to determine output drive

strength.

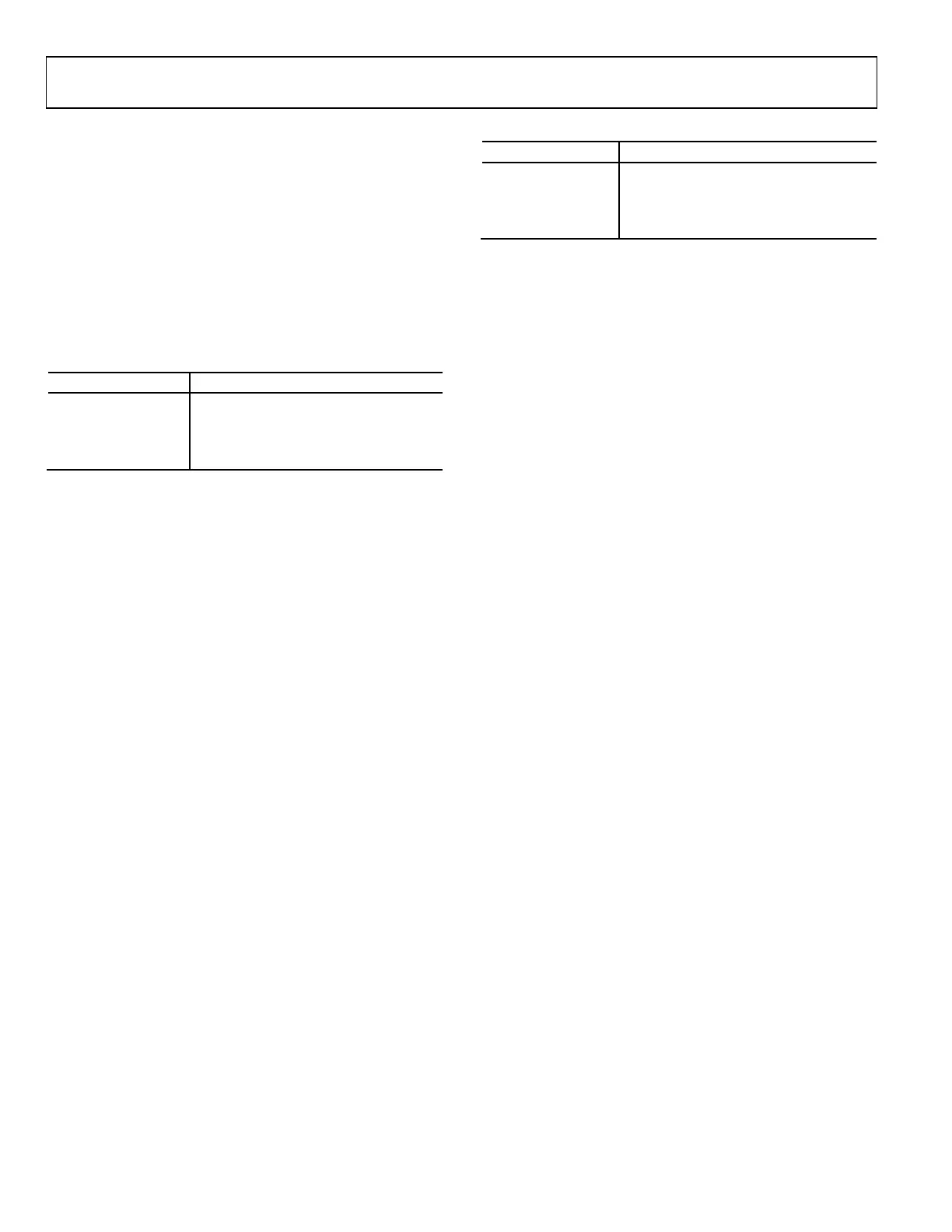

Table 10. Output Logic Type, Register 0x014 Bits[7:6]

00 Option 0

01 Option 1

10 Option 2

11 Option 3

Bit 5—Output Multiplexer

If Bit 5 is set, the output is muxed between two different outputs

or it interleaves two ADCs on the same output in a double data

rate fashion.

Bit 4—Output Enable

Bit 4 is the output enable. If this bit is low, the output is enabled.

For CMOS/TTL devices, this places the output in high impedance

state. For other logic families, the output is placed in a mode

defined by the device data sheet. If an external output enable exists,

then the function of this bit is defeated. If an external pin is defined

as an alternate function (see the Modes (0x008) section), then this

bit controls the output.

Bit 3—Double Data Rate Enable

Bit 3 allows fewer output pins to be used to produce the same

amount of data. When this bit is set, all data bits are sent using

one-half of the output bits, but clocked at twice the sample rate.

The remaining output bits are unused in this mode. When this

bit is clear, the converter behaves in a normal manner with all

output bits being used.

Bit 2—Output Invert

Bit 2 inverts the outputs when set.

Bit 1 to Bit 0—Output Coding

Bit 1 to Bit 0 determine the output coding.

If set to:

• 00, the output is offset binary.

• 01, the output is twos complement.

• 10, the output is gray code.

11 is reserved.

Only modes supported by the individual device are recognized.

(See the device data sheet.) The default is 0x00.

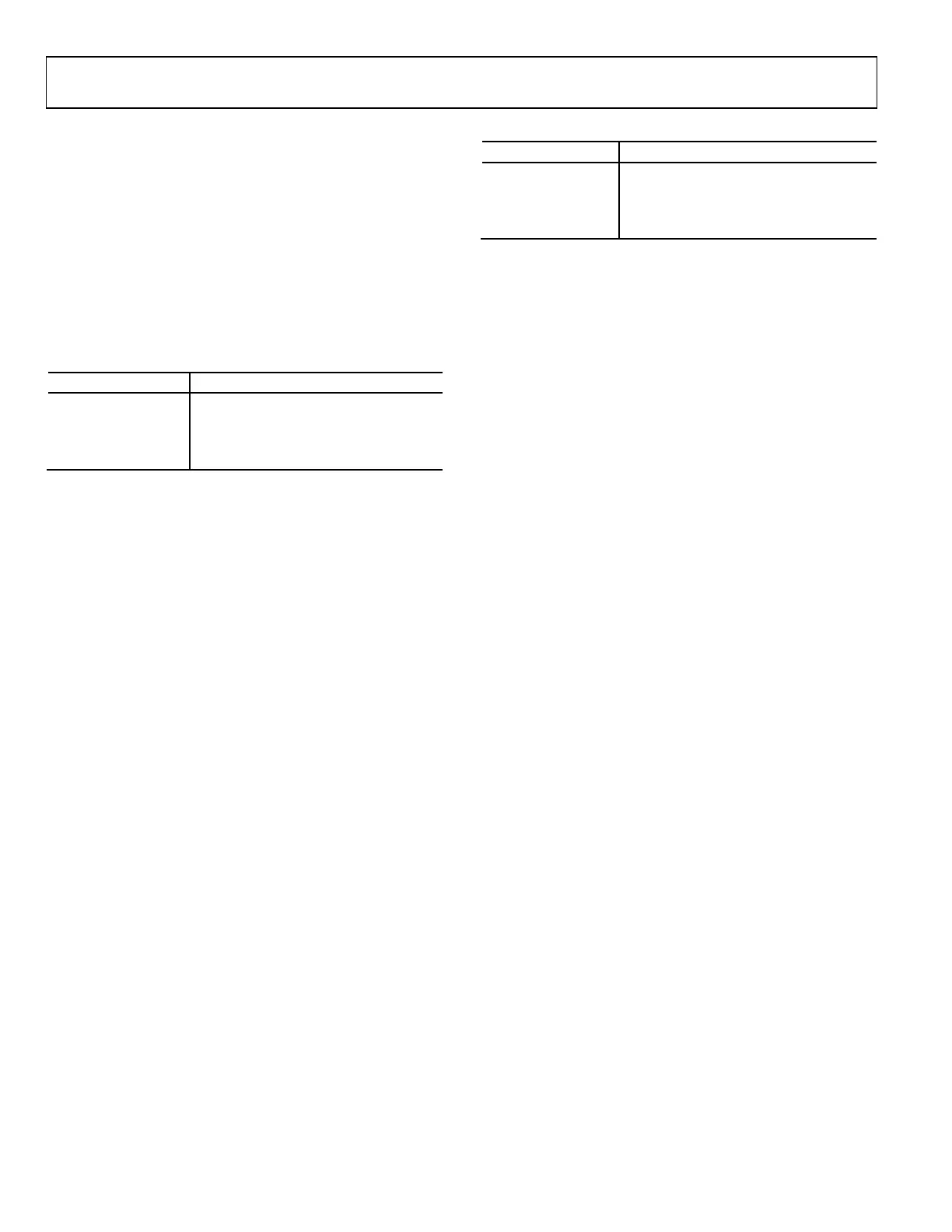

Table 11. Output Format, Register 0x014, Bits[1:0]

Bit 1 to Bit 0 Output Data Format

00 Offset binary

01 Twos complement

10 Gray code

Output Settings (0x015)

Register 0x015 works with CMOS and LVDS modes to set

output termination and output driver current levels.

Bit 7 to Bit 4—Output Termination

Bit 7 to Bit 4 determine the output termination options for

LVDS and other controlled impedance driver outputs (see the

device data sheet for more details).

Bit 3 to Bit 0—Output Drive Current

Bit 3 to Bit 0 determine the output drive current for various

CMOS and LVDS options (see the device data sheet for more

details).

Clock Divider Phase (0x016)

Registers 0x016 determine which phase of the clock divider is

used to latch data. This can be used in conjunction with either

Register 0x00B or with a PLL divider output used to supply a

serial clock. The default for this register is 0x00, selecting the

first phase not inverted.

Bit 7—Phase Invert

Bit 7 inverts the internal phase.

Bit 6 to Bit 4—Reserved

Bit 3 to Bit 0—Phase Select

Bit 3 to Bit 0 determine which phase is selected to drive the

serial clock.

Output Delay Adjust (0x017)

Register 0x017 sets the fine delay in the output latch relative to

when the internal output registers are strobed. Internal timing is

not altered by this setting. Only the output latch is changed to

compensate for any external setup and hold time issues

resulting from ADC timing issues. The range of this register is

specified in the device data sheet.

Bit 7—Enable

For this feature, Bit 7 acts as an enable. If clear, default timing is

selected providing reference timing.

Bit 6—DLL Enable

Setting Bit 6 enables an on-chip delay locked loop (DLL) that is

used in the generation of the output latch. The DLL is used to

maintain optimal timing between the output data eye and the

latch for that data. This is useful in applications where timing is

critical and data must be optimized. If this bit is clear, the DLL

is off and the delay may be manually adjusted by Bit 5 to Bit 0

when enabled with Bit 7.

Loading...

Loading...