35

ATtiny15L

1187H–AVR–09/07

1. In the same operation, write a logical “1” to WDTOE and WDE. A logical “1” must

be written to WDE even though it is set to one before the disable operation starts.

2. Within the next four clock cycles, write a logical “0” to WDE. This disables the

Watchdog.

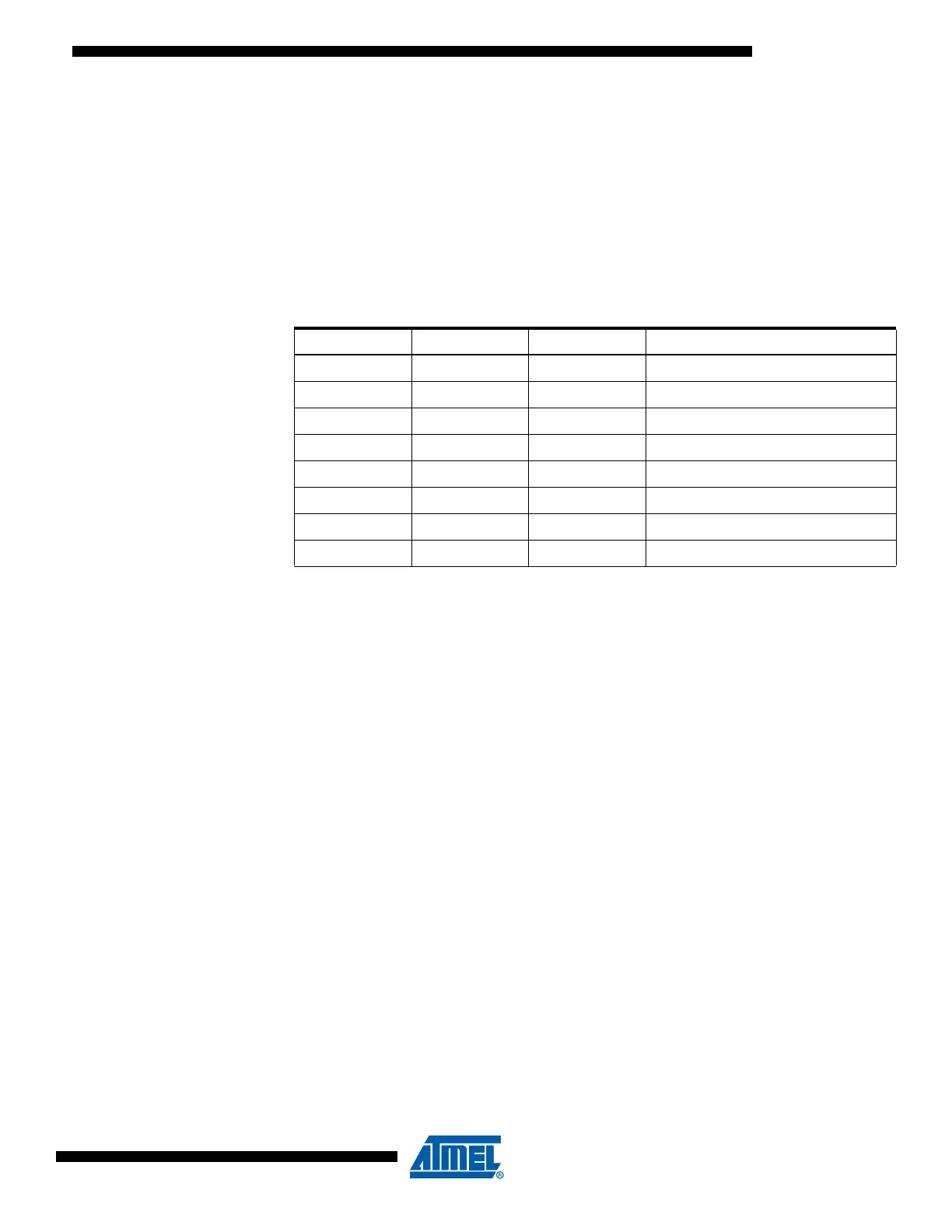

• Bits 2..0 – WDP2, WDP1, WDP0: Watchdog Timer Prescaler Bits 2, 1, and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the

Watchdog Timer is enabled. The different prescaling values and their corresponding

time-out periods are shown in Table 15.

Table 15. Watchdog Timer Prescale Select

WDP2 WDP1 WDP0 Time-out Period

0 0 0 16K cycles

0 0 1 32K cycles

0 1 0 64K cycles

0 1 1 128K cycles

1 0 0 256K cycles

1 0 1 512K cycles

1 1 0 1,024K cycles

1 1 1 2,048K cycles

Loading...

Loading...