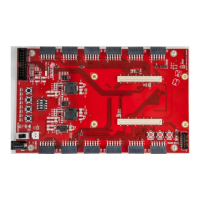

4 MicroZed IOCC Key Features

– Expansion connectors

– 12 Digilent Pmod™ Compatible headers

– Five connected to PL Bank 34

– Four connected to PL Bank 35

– One connected to PS MIO

– Two connected to PL Bank 13 (7Z020 only)

– Xilinx Agile Mixed Signaling (AMS) header

– Clocking

– 100 MHz clock source for PL

– Configuration and Debug

– Xilinx Platform Cable JTAG connector

– General Purpose I/O

– 8 user LEDs

– 4 push buttons

– 4 DIP switches

– Memory

– Optional footprint: 1KB 1-wire SHA Security EEPROM (not populated)

Loading...

Loading...