PCIE_CLK_SB# 14

PCIE_CLK_NB#

C207 *10P_50V_04

C1 5 7

.1U_16V_04

Mobile mode

CL K_ 4 8M _C ARD

R106 22_04

BSE L2

CPU _BSEL 1 2

PC IE_C L K_SB_R

R 302 22_04 C151 *10P_50V_04

PECLKREQ1#

EM I 1/ 3

H_ CL K_ CPU #

CLK_12M _U SB

S_C LK9,10,14,20

PC IE_C L K_N EW # _R

R67 33_04

1.8VS

PC IET_ L 1

CL K_ 48 M_C ARD 2 2

Z_CLK1

M_ C LK_ DD R0 # _R

M_ C LK_ DD R1 # _R

C165 *10P_50V_04

CPU_STOP#

1 2 00 MH z

3.3VS 6,10,11,12,13,14,15,16,18,19,20,21,22,24,25,26,27,28

CL K_ S ATA 15

M_ CL K _ DD R1

BS EL 0

M_ C LK _ DD R 2 #

C LK_ SATA_ R

C231 *10P_50V_04

R6 5 0 _0 4

CLK_STOP#

CLK_14M_968 14

C525 *10P_50V_04

C143 *10P_50V_04

CL KGEN _VD D

H_CLK_CPU_R

H_ CL K_ NB

C1 3 0

.1U_16V_04

3.3VS

PCIE_CLK_HD V# 11

CLKGEN_MODE

C149 *10P_50V_04

R3 26 2 .2 K_0 4

RESET#

(HI)PULLl-UP

C161 *10P_50V_04

EM I 1/3

M_CLK_DDR 3 10

CLKEN

R309 * 10K_04

Status

1

H_ CL K_ CPU 2

Z1707

CL KB U F _AV DD

M_CLK_DDR 0# 9

C215 *10P_50V_04

PCIE_CLK_NB

C LKG EN_FSL 2

C234 *10P_50V_04

R299 0_04

R 311 33_04

R6 6 * 2.7 K _ 0 4

PCI_STOP#Pin 12

CPU _BSEL 0 2

PC IE_C LK_H DV#_R

PC IE_C L K_N B_R

PC IE_C L K _M INI# _ R

R 301 33_04

1

3.3VS

CL K_ 12 M_U SB 15

RN 11

4P2R X33_04

1 4

2 3

L4 5

H CB1005KF-121T20

Mode

C2 2 7

10P_50V _04

0

H_ CL K_ CPU # 2

Z1706

FB_IN A

M_ C LK_ DD R3 # _R

PC LK_DE BUG_R

M_ C LK _ DD R 0 #

CL K_ S AT A

L12

HCB1005KF-121T20

R3 17 2 .2 K_0 4

1

PCIE_CLK_HD V 11

CL K _ SA TA #

Z_CLK1 1 3

M_ CL K _ DD R0 #

H_CLK_NB#_R

C228 *10P_50V_04

Pin 28

PCICLK6

PCLK_ CAR D 2 2

PCLK_ SB

M_ C LK_ DD R2 _ R

C2 2 4

.1U_16V_04

RN 12

4P2R X33_04

1 4

2 3

C531 *10P_50V_04

C1 7 4

.01U _16V_X7R _04

3. 3 V S

M_FWDSDCLKOA_D#5

PCIE_CLK_MIN I 20

RN8

4P2RX0_04

1 4

2 3

Ho st Cl oc k

CLKGEN_FSL2

R307 10K_04

C132 *10P_50V_04

1

C L K _ 14 M _ 6 7 1M X

CL K _ 14 M_9 6 8

PC IE_C LK_SB#_R

C2 1 2

.1U_16V_04

C2 1 8

.1U_16V_04

M_ C LK _ DD R 1 #

Clock Generator Pin 15

M_ CL K _ DD R1 #

CLKGEN_FSL1

KBC_PC LK

L9

H CB1005KF-121T20

C128 *10P_50V_04

H_ CL K_ NB# 4

CLK_14M _671MX

C122 *10P_50V_04

1

PCLK_ CAR DCLKGEN_FS4

R305 10K_04

1

4 /12

M_CLK_DDR 1# 9

PCIE_CLK_SB

C5 00

10U_10V_08

RN 17

4P2R X33_04

1 4

2 3

R 327 10K_04

PCIE_CLK_MIN I

M_ C LK _ DD R 3 #

X3

HSX53 1 S_14 .3 1 8M Hz

12

34

C2 3 3

10U _10V_08

Fr eq uen cy

PCLK_ SB 1 3

H_ CL K_ NB 4

1

CL K _ SA TA

PCICLK3

FS3

3.3VS

M_ CL K _ DD R3

PC IE_C L K_H DV_R

PCLK_ LPC RO M

R6 3 0 _0 4

VTTOWRGD/PD#

C LKEN #28

H_ CL K_ CPU

CLK_14M _968

C137 *10P_50V_04

0 0

MINI_CARD_CLKREQ# 20

PCIE_CLK_NEW# 20

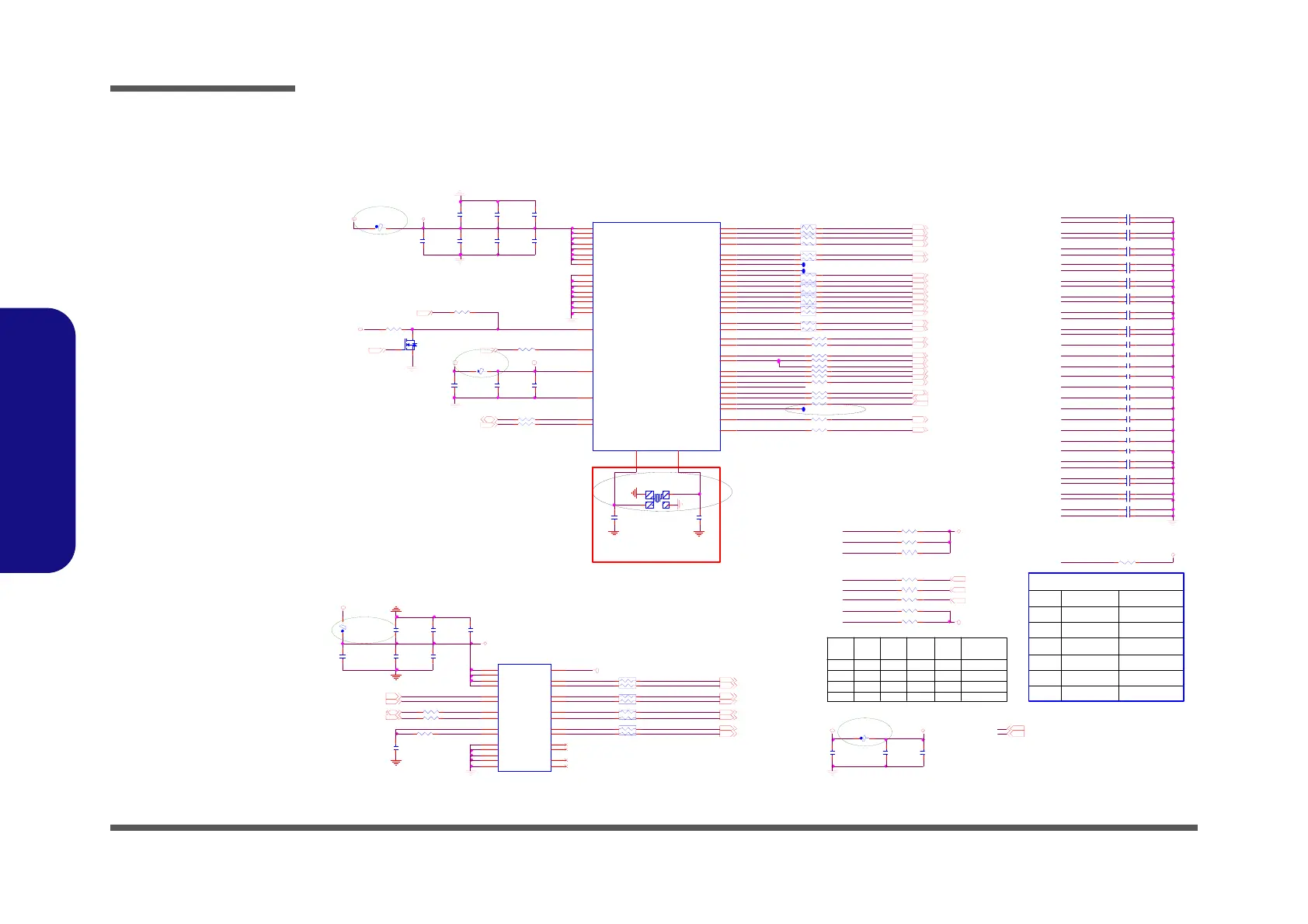

U1 1

ICS9P93 5

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17 16

15

DD RC0

DDRT0

VD D1.8

DDRT1

DD RC1

GND

VDD A1.8

GND

CLK_INT

CLK_INC

VD D1.8

DDRT2

DD RC2

GND

GND

DD RC5

DDRT5

VD D1.8

GND

DD RC4

DDRT4

VD D1.8

SD ATA

SC LK

FB_IN

FB_OUT DDRT3

DD RC3

3.3VS

M_CLK_DDR 0 9

PCLK_ SB

RN7

4P2RX0_04

1 4

2 3

C5 32

33P_50V_04

PCICLK5

0

FS4

PCIE_CLK_NB# 4

C L K _ 14 M _ 3 0 7E L V

M_ C LK_ DD R0 _ R

CLK_12M_USB_R

R60 10K_04

M_ C LK_ DD R1 _ R

C127 *10P_50V_04

C208 *10P_50V_04

R 323 33_04

CL K_ S ATA # 1 5

M_CLK_DDR 3# 10

M_ CL K _ DD R2

1

0

CLKBUF_AVDD

CPUSTP#6

PCLK_ L PCRO M

C LK_ SATA# _R

H_CLK_CPU#_R

R 303 22_04

PCIE_CLK_NEW 20

C191 *10P_50V_04

C2 2 5

.1 U_ 16 V_ 0 4

0

KBC_PCLK 26

R104 *0_04

R 306 0_04

PCIE_CLK_NB 4

STP_ PCI#

C168 *10P_50V_04

C175 *10P_50V_04

S_D AT9,10,14,20

C LKG EN_FSL 1

RN 14

4P2R X33_04

1 4

2 3

M_ C LK_ DD R3 _ R

RN 19

4P2R X33_04

1 4

2 3

L13

HCB1005KF-121T20

C187 *10P_50V_04

C158 *10P_50V_04

100 MHz

FB_O UTA

PCIE_CLK_HD V

Z1703

R308 *0_04

M_ CL K _ DD R0

Z1702

CL K GEN _M OD E

R 321 33_04

C169 *10P_50V_04

BS EL1

PCIE_ CL K_ MIN I# 20

PCIE_CLK_SB#

CL K _ 48 M_C ARD

C1 6 4

1U_10V_06

C1 8 8

.1U_16V_04

C527 *10P_50V_04

M_CLK_DDR 2# 10

PEC LK REQ0 #

CL K _ 12 M_U SB

Z_CLK0_R

H_ CL K_ NB#

M_CLK_DDR 2 10

PEC LK REQ1 #

H_CLK_NB_R

R3 10 2 .7 K_0 4

C182 *10P_50V_04

0

0

PC IE_C L K_N EW _ R

Z_CLK1

Z_CLK0

C LKG EN_FS3

C1 5 2

.1U_16V_04

RN9

4P2RX0_04

1 4

2 3

0

M_ C LK _ DD R 1

PC IE_C L K_N B#_R

RN 20

4P2R X33_04

1 4

2 3

C1 8 0

.1U_16V_04

Pin 1

CLK_ 14 M_ 3 0 7EL V 1 1

R 319 33_04

C153 *10P_50V_04

C2 14

10U_10V_08

CPU _BSEL 2 2

KBC_PCLK

3/20

Z1704

R62 *33_04

1

PC IE_C L K _M INI_ R

CLKGEN_FS3

CLKBUF_VDD

C2 2 2

.01U_16V_X7R _04

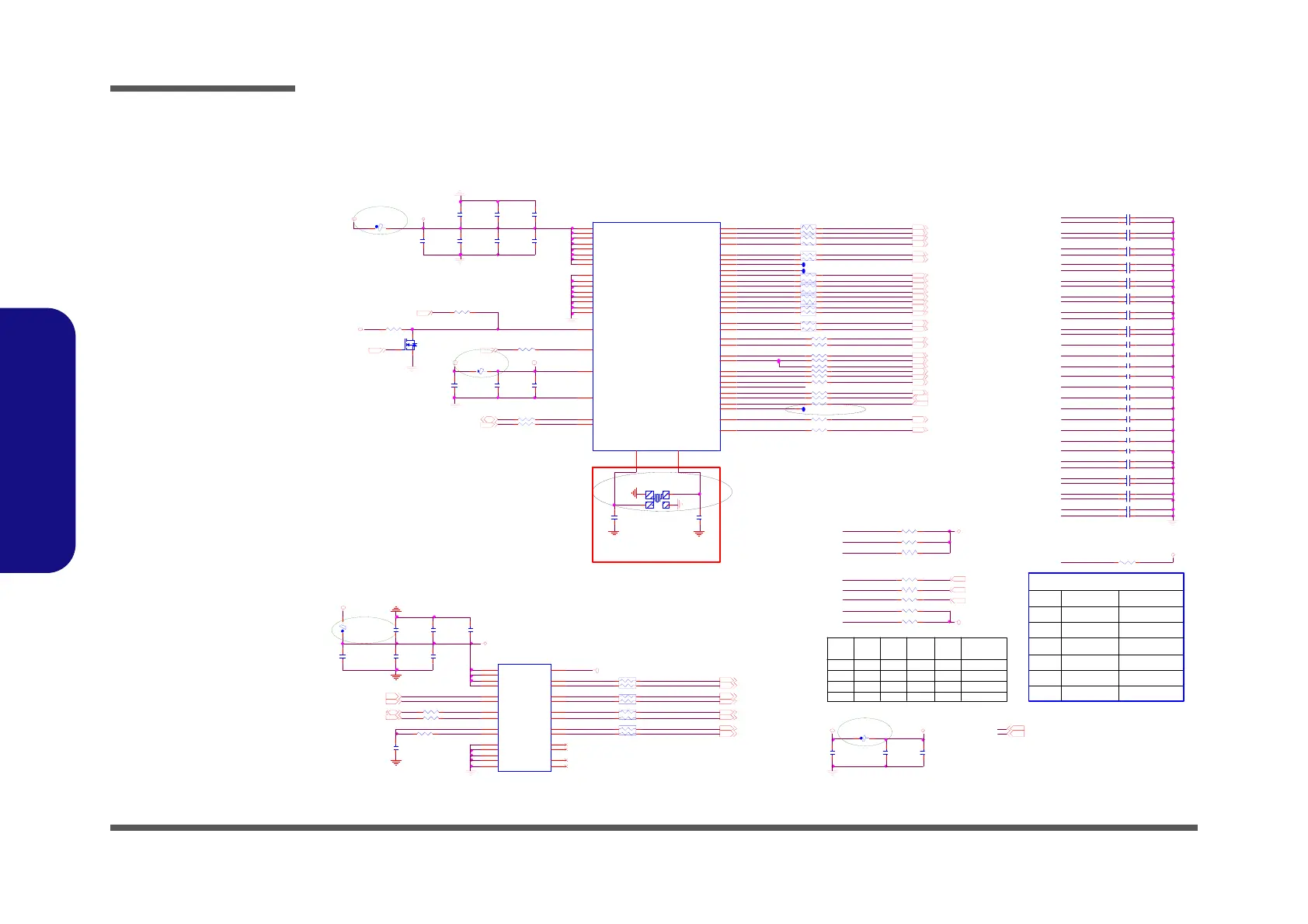

U31

ICS9LPR600C GLF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

(CLK_STOP#)/VTTPWR GD /PD#

VDD REF

**FSL0/R EF0_2x

*FSL1/R EF1_2x

X1

X2

GN DR E F

GN DP C I

** F S L2 /P C I CL K0 _2 x F

**F S 3 / P C I C L K 1 _2 x F

** F S 4/ P C I C L K 2

*(PC I_STO P#)/PC ICL K3

GN DP C I

VDD PCI

**MO DE/PC ICLK4

(PE CL K RE Q 0 #)/ P C ICL K 5

(PE CL K RE Q 1 #)/ P C ICL K 6

PC ICLK7

VDD PCI

GN DZ

ZCLK0

ZCLK1

VDD Z

VDD 48

12MHz

**SEL24_48#/24_48MHz

GN D4 8

*(C PU_STOP#)/RESET#

VDD CPU

CPU T_L0F

C PUC _L0F

GN DC P U

CPU T _L 1

CPUC_L1

VDD A

SATAC LKT_ L

SATACLKC_L

GN DA

SCLK

SDATA

PC IET_L 0

PCIEC _L 0

GN DP C I E X

PC IET_L 1

PCIEC _L 1

VDD PCIEX

PC IET_L 2

PCIEC _L 2

PC IET_L 3

PCIEC _L 3

PC IET_L4F

PCIEC _L4F

GN DP C I E X

PC IET_L5F

PCIEC _L5F

VDD PCIEX

166 MHz

EM I 1 /3

1. 8 V S

PCLK_ LPC RO M

M_ C LK _ DD R 0

M_CLK_DDR 1 9

M_ C LK _ DD R 3

C144 *10P_50V_04

Place CRYSTAL Within 500

mils of ICS9LPR600

NEW_CAR D_CLKR EQ# 20

M_ CL K _ DD R3 #

CLK_14M _307ELV

Q7

2N7002W

G

DS

R3 13 2 .2 K_0 4

CLKGEN _VD DA

PCIE_CLK_HD V#

SEL24_ 48 #

CL K_ S AT A #

C533

33P_50V_04

C535 *10P_50V_04

PECLKREQ0#

SU SB#1 8 , 2 0, 2 2 , 27 , 3 0 , 31

M_ CL K _ DD R2 #

PEC LKR EQ0 #

C1 3 4

10U _10V_08

C177 *10P_50V_04

3. 3 V S

M_ F W D S D C LK O A _D5

1 .8 V S 4 ,5,6 ,7 ,1 1,1 2 ,13,1 4 ,15 ,1 6 ,27

PCLK_ CAR D

Z_CLK1_R

CLKGEN_FSL0

R 300 33_04

PC IEC_ L 1

M_ C LK _ DD R 2

STP_ PCI#

R3 2 8 *0 _ 04

S_CLK9,10,14,20

Z1701

C518 *10P_50V_04

Z 1705

RN 15

4P2R X33_04

1 4

2 3

S_DA T9,10,14,20

PCIE_CLK_NEW#

M_ C LK_ DD R2 # _R

Z_CLK0

RN10

4P2RX0_04

1 4

2 3

0

E MI 1/ 3

R 314 33_04

PCIE_CLK_NEW

(LO)Non-STUFF

C LKG EN_FSL 0

C235 *10P_50V_04

C2 1 3

.1U_16V_04

CLK_14M_671M X 6

PEC LKR EQ1 #

C1 8 4

1U_10V_06

Pin 16

C141 *10P_50V_04

133 MHz

RN 21

4P2R X33_04

1 4

2 3

Pin 17

PCIE_CLK_MIN I#

C209 *10P_50V_04

R105 *0_04

C2 3 2

.1 U_ 16 V_ 0 4

C167 *10P_50V_04

Desktop mode

Z_CLK0 6

PCIE_CLK_SB 14

C LKG EN_FS4

Loading...

Loading...